# 研究成果報告書

高性能SiCパワーデバイスを活用した大電力パルス電源小型化のための研究

令和6年5月 株式会社日立製作所 本報告書は、防衛装備庁の安全保障技術研究推進制度による委託業務として、株式会社日立製作所が実施した令和5年度「高性能SiCパワーデバイスを活用した大電力パルス電源小型化のための研究」の成果を取りまとめたものです。

# 1. 委託業務の目的

本委託業務では、小型・高性能なパルス電源の実現を目的とした高耐圧 SiC スイッチング素子開発に関する基礎研究を実施する。大電力パルス電源用途のスイッチング素子としては、高速・高耐圧・大電流容量などの基本特性に加え、高過負荷耐性、高信頼性などの性能が要求されるが、これらの要求に応える高耐圧 SiC スイッチング素子を新たに開発することで、従来の Si スイッチング素子では達成できないパルス電源の小型・高性能化を狙う。

耐圧数 kV 級の SiC スイッチング素子は世の中で使われだしているものの、本研究で目標とする耐圧 10kV 級の SiC スイッチング素子の実用化は全く進んでいない。その主な要因は SiC エピ膜中に存在する結晶欠陥による歩留まり・信頼性低下にあり、その課題を解決しない限り高耐圧 SiC スイッチング素子の実用化は困難である。耐圧 10kV 級の SiC スイッチング素子が実現できれば低耐圧素子の多段直列接続や、昇圧トランスが不要になりシステムの大幅な小型化が期待できる。

上記課題認識のもと、本研究では下記に示す最終目標を掲げて研究開発を推進し、最終的に大電力パルス電源実現に資する高耐圧 SiC スイッチング素子を実現することを目指す。

# ①大電カパルス電源用高耐圧 SiC スイッチング素子開発

高速・低損失な SiC 絶縁ゲートバイポーラトランジスタ (IGBT) の実現を目的に SiC エピ積層構造・キャリアライフタイムとデバイス設計への適用手法を確立し、そのキャリアライフタイム実現のための SiC エピ成膜技術、およびデバイスプロセス技術を研究する。加えて、通電劣化現象抑制のために起点となる基底面転位が発生する条件を明らかにすることにより、所定の性能を有する高信頼 SiC IGBT の実現を目指す。この SiC IGBT を用いてパルス電源の要素回路を試作し、パルス出力波形を評価することでライフタイムの最適化、駆動方式の最適化を行い、小型・高信頼なパルス電源に関する知見を得ることを目標とする。

本研究において目標とする SiC IGBT の性能は、以下のとおりである。

- 耐圧 10kV 以上

- ターンオフ時の電流立下り時間 50ns 以下

- オン電圧 5 V 以下(150°C、コレクタ電流 100A/cm²時)

- コレクタ電流 100 A/cm²を 1000 時間通電時のオン電圧の変動が 1 %以下

- ミニモデルによるパルス出力評価:パルスピーク電流1 kA を目標とする。

### ②ジャスト基板を用いたエピ膜成長技術

オフ基板上へのエピ膜成長という従来のアプローチに対して、ジャスト基板上へのエピ成長技術を新たに確立することで、デバイス特性劣化を引き起こす主要因となっている基底面転位 (BPD) の密度をゼロにするとともに、耐圧歩留まりの低下を引き起こす 3C インクルージョンの密度を 0.2 個/cm² 以下を達成することを目指す。またデバイスの電流容量に直結するキャリアライフタイムは、エピ膜成長後のプロセス適用も含めて、 $2\mu$  sec 以上を達成することを目指す。加えて、既に産業技術総合研究所、及び電力中央研究所が有するオフ基板上で BPD 密度を低減する技術 (再結合促進層導入等)を活用した信頼性向上技術を検証する。上記目標を達成する際の条件として、エピ膜厚、及び不純物濃度は、10~kV~以上の耐圧設計を想定し、それぞれ  $150~\mu$ m 以上、5.0x  $10^{14}$ /cm² 以下とする。開発したエピ成長技術の効果を検証するために、SiC サイリスタを設計、作製する。

# ③SiC エピ膜中の結晶欠陥のモデル化ならびにキャリアライフタイム制御技術

SiC デバイスの大電流パルス出力性能を向上することを目的とした SiC エピ膜中の結晶欠陥のモデル化ならびにキャリアライフタイム制御技術に関する基礎研究を実施する。このため、まず

は SiC エピ膜のキャリアライフタイムを制御する再結合中心ならびに SiC デバイスの電流出力性能を低下させる SiC エピ膜中の積層欠陥などの結晶欠陥を対象として、それらの物理的パラメータを実験的に求める。次に得られたパラメータを用いて、キャリア再結合や積層欠陥のモデル化を行い、これらのモデルを SiC エピ膜とデバイスの設計・試作に反映させることで、大電流パルス出力 SiC デバイスの性能向上に対する指針を与えることを目標とする。

本研究において、主に対象とする結晶欠陥は以下の通りである。

- ・SiC エピ膜中の再結合中心(窒素、バナジウム、アルミ、ボロン、炭素空孔、それらの複合欠陥)

- ・SiC エピ膜中の積層欠陥 (ショックレー型積層欠陥、フランク型積層欠陥)

これらの結晶欠陥を制御することで、大電流パルス出力と積層欠陥拡大(通電劣化現象)の抑制を両立するための SiC エピ膜を作製可能とする。

具体的には下記7項目を実施した。(⑦は欠番)

- ① SiCエピ積層構造・ライフタイム制御と高速スイッチングSiC IGBTデバイス設計への適用手の確立(担当: (株)日立製作所)

- ② SiC IGBT通電劣化現象の解明と抑制(担当: (株)日立製作所)

- ③ ジャスト基板を用いたエピ膜成長技術開発(担当: (国研)産業技術総合研究所)

- ④ SiCサイリスタによるエピ膜品質評価(担当: (国研)産業技術総合研究所)

- ⑤⑥ 大電流パルス動作時におけるキャリア再結合のモデル化とキャリアライフタイム制御(担当:(一財)電力中央研究所、(株)日立製作所)

- ⑧⑨ 大電流パルス動作時における積層欠陥のモデル化と電気特性への影響評価(担当:(一財)電力中央研究所、(株)日立製作所)

- ⑩⑪ 超高耐圧SiC IGBTを用いた大電力パルス電源高速・高信頼駆動手法の確立(担当:(株) 日立製作所、(国研)産業技術総合研究所)

2. 研究開始時に設定した研究目標の達成度

研究目標①大電カパルス電源用高耐圧 SiC スイッチング素子開発に対し、

- · 耐圧 10kV 以上

- ・ ターンオフ時の電流立下り時間 50ns 以下

- オン電圧 5 V以下(150°C、コレクタ電流 100A/cm²時)

- ・ コレクタ電流 100 A/cm<sup>2</sup> を 1000 時間通電時のオン電圧の変動が 1 %以下

- ミニモデルによるパルス出力評価:パルスピーク電流 1 kA (パルス幅)

の目標全てを達成し、達成度100%である。

研究目標②ジャスト基板を用いたエピ膜成長技術に対し、

- ・3Cインクルージョン密度 < 0.2個/cm<sup>2</sup>以下、

- ・キャリアライフタイム2μsec以上

- ・PiNダイオードを作製することによりエピ膜の品質評価

の目標の内、30 インクルージョン密度の低減は 0.8 個/cm2 の達成にとどまり目標達成に至らなかった。ただし、残存する 30 インクルージョン発生原因については膜成長途中のパーティクルが原因であることは解明できており、炉内のグラファイト部材を定期的にクリーニングすることで 0.2 個/cm2 以下に低減する技術的な目途はつけることができた。全てを達成し、達成度 100%である。その他の目標については達成した。

研究目標③SiC エピ膜中の結晶欠陥のモデル化ならびにキャリアライフタイム制御技術に対し、 実施項目⑤大電流パルス動作時におけるキャリア再結合のモデル化とキャリアライフタイム制御 (担当: (一財) 電力中央研究所) および⑧ 大電流パルス動作時における積層欠陥のモデル化 と電気特性への影響評価(担当: (一財) 電力中央研究所) を実施した。

SiC デバイスの大電流パルス出力性能を向上することを目的とした SiC エピ膜中の結晶欠陥のモデル化ならびにキャリアライフタイム制御技術に関する基礎研究を実施し、SiC エピ膜のキャリアライフタイムを制御する再結合中心ならびに SiC デバイスの電流出力性能を低下させる SiC エピ膜中の積層欠陥を対象として、それらの物理的パラメータを実験的に求めた。得られたパラメータを用いて、キャリア再結合と積層欠陥のモデル化を行い、大電流パルス出力(1 kA/cm²以上)SiC デバイスの性能向上に対する指針を得た。計画通りに進捗し、研究開始時に設定した研究目標を達成し、達成度は 100%である。

# 3. 委託業務における研究の方法及び成果

# ①SiCエピ積層構造・ライフタイム制御と高速スイッチングSiC IGBTデバイス設計への適用手法の確立(担当: (株)日立製作所)

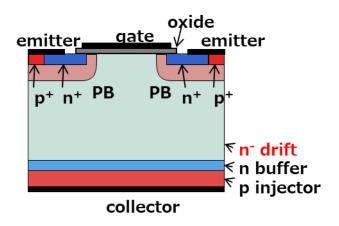

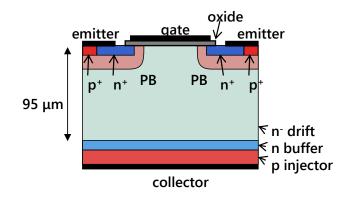

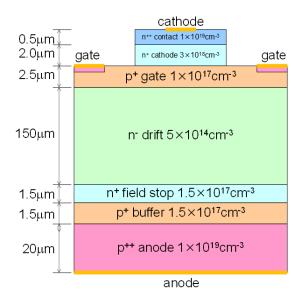

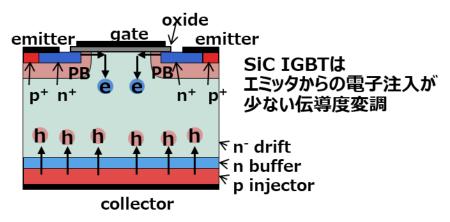

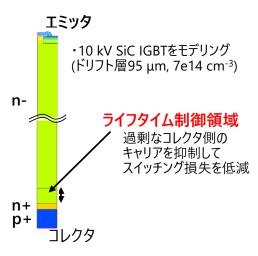

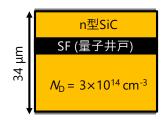

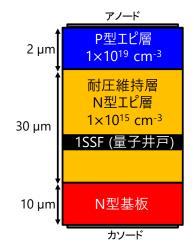

デバイスシミュレータを用いて、耐圧10 kV以上を達成するSiC IGBT構造(図1-1) デバイス・エピ構造・アクティブセル構造・キャリアライフタイム制御設計を実施した。

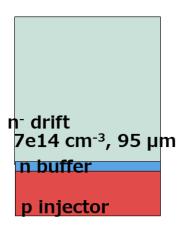

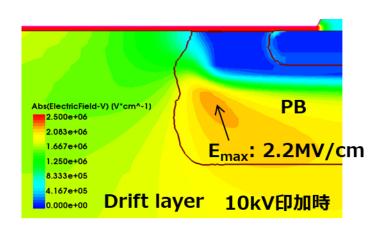

エピ構造設計においては、エピ濃度・膜厚ばらつきを考慮した耐圧確保、ボディ層 (PB) 端部での電界集中による耐圧低下が課題である。耐圧10kVを実現するエピ構造を決定し(図1-2)、10 kV印加時の最大電界は (2.2 MV/cm)と絶縁破壊電界以下であり、ばらつきを考慮しても実デバイス構造において耐圧確保が可能であることを示した(図1-3)。

図1-1 SiC IGBT アクティブセル断面図

図1-2 検討したSiC IGBTエピ構造

図1-3 耐圧が最小となるドリフト層ばらつき時のアクティブセル内 (ボディ層付近) 電界分布(濃度+25%、膜厚-10%を想定)

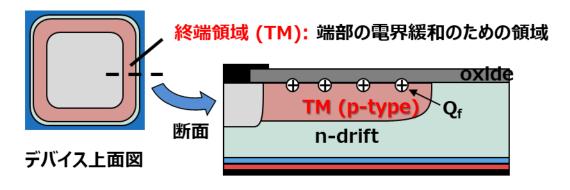

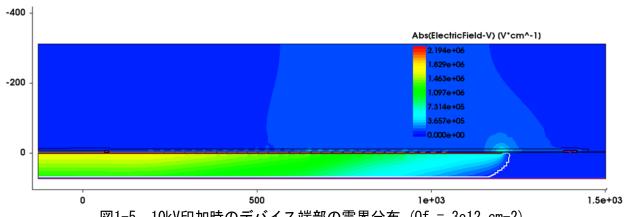

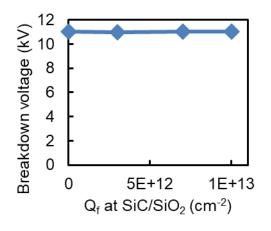

アクティブセル構造設計においては、端部での電界集中を緩和する終端領域の濃度分布・幅の設計・耐圧保持ストレスによる $Q_f$  ( $SiC/SiQ_2$ 界面の電荷)変動対策が課題である (図1-4)。設計したデバイス終端構造において、10 kV印加時のデバイス端部の電界分布 ( $Q_f = 3e12 \text{ cm}-2$ )を計算し、SiC中の電界は絶縁破壊電界より小さい1.7 MV/cm以下に収まっており、端部での電界集中を緩和できていることを示した (図1-5)。さらに、実際にデバイス動作で想定している界面電荷量 ( $Q_f = 13 \text{ cm}-2$ )の範囲において、耐圧10 kV以上を達成できることを示した (図1-6)。

図1-4 デバイス終端構造設計

10kV印加時のデバイス端部の電界分布 (Qf = 3e12 cm-2)

図1-6 Qfに対する終端部の耐圧の変化

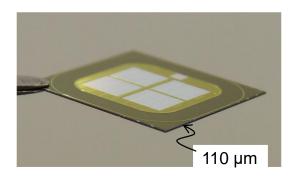

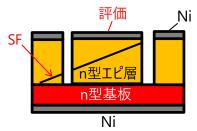

設計したSiC IGBTのエピ構造・アクティブセル構造を適用して、外部調達ウェハによる実デバイス の試作を実施した。試作にあたっては、裏面加工プロセスを適用した。SiCではn型基板しか存在せ ず、その基板上にn, p型のエピタキシャル層を成長してデバイス構造を形成する。したがって、図1-7に示すようなSiC IGBTの場合、裏面のp型注入層を露出させるためには、下地のn型基板をすべて研 削して、層厚110 um程度の薄膜ウェハのデバイスを作製する必要がある。この裏面加工を実現する プロセスを適用し、図1-8に示すような10 mm角のSiC IGBTチップの作製に成功した。

図 1-7 SiC IGBT アクティブセル断面図

図 1-8 SiC IGBT 試作チップ写真

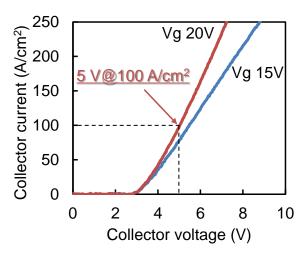

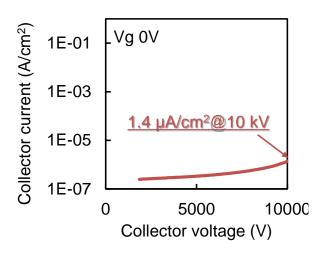

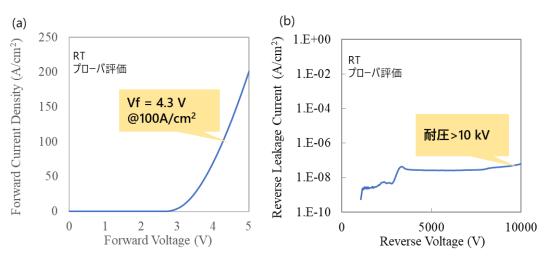

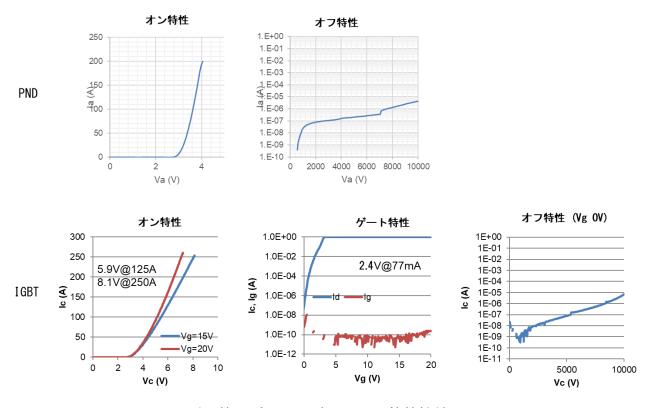

試作したSiC IGBTについて、デバイス特性を評価した。図1-9にデバイスオン時のコレクタ電流 -電圧特性を示す。SiC IGBTとしての伝導度変調によるバイポーラ動作が確認でき、本テーマにおける目標であるコレクタ電流100 A/cm²におけるオン電圧5 Vを達成した。図1-10にデバイスオフ時(ゲート電圧0 V)のコレクタ電流 - 電圧特性を示す。コレクタ電圧10 kV印加時のリーク電流は1.4  $\mu$ A/cm²であり、試作したSiC IGBTにおいて10 kV耐圧を達成した。

図 1-9 SiC IGBT のオン時の コレクタ電流 - 電圧特性

図 1-10 SiC IGBT のオフ時の コレクタ電流 - 電圧特性

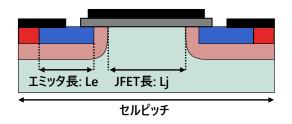

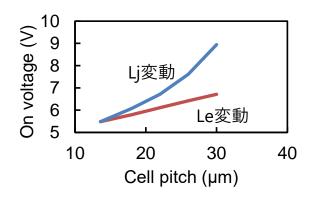

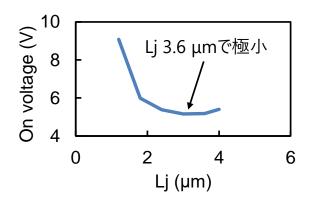

また、SiC IGBTについて、デバイスレイアウトが性能に与える影響の検討を実施した。デバイス設計においては、図1-11に示すような、セルピッチやJFET長(L<sub>j</sub>)、エミッタ領域の長さ(L<sub>e</sub>)といったレイアウト寸法がオン電圧に与える影響を明らかにし、設計指針の確立が課題となる。特にIGBTにおいてはMOSFETと異なり、キャリア注入による伝導度変調がオン電圧に影響するため、IGBTに特有の設計指針を見出す必要がある。セルピッチとオン電圧の関係について、JFET長とエミッタ長を変動させた場合の結果を図1-12に示す。セルピッチを小さくするとオン電圧が減少し、特にエミッタ長よりもJFET長を縮小したほうが、オン電圧低減効果が高いこと見出した。また、図1-13に示すように、JFET長を減少していくと、オン電圧は極小値を持ち、より縮小するとオン電圧は逆に増大することを明らかにし、SiC IGBTのレイアウト設計指針を示した。

図 1-11 SiC IGBT アクティブセルのレイアウト寸法

図 1-12 セルピッチとオン電圧の関係

図 1-13 JFET 長 (Lj) とオン電圧の関係

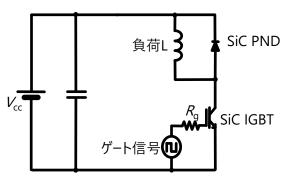

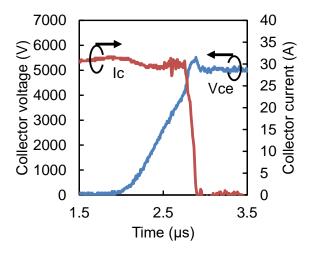

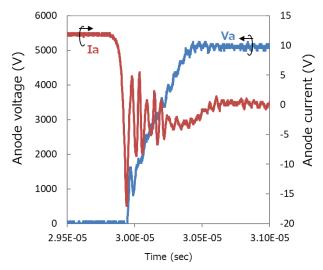

試作した SiC IGBT について、静特性に加えてスイッチング特性を評価した。図 1-14 に示す評価回路を用い、ダブルパルス試験によるターンオフおよびターンオン特性を測定した。図 1-15 にターンオフ特性、図 1-16 にターンオン特性を示す。試作したデバイスは正常にスイッチングしており、ターンオフ時の電流立下り時間 50ns 以下を達成、本研究で設計した SiC IGBT のデバイス動作を実証した。

図 1-14 スイッチング特性評価回路

7000 (>6000 95000 95000 3000 1 3 5 Time (μs)

図 1-15 SiC IGBT ターンオフ特性

図 1-16 SiC IGBT ターンオン特性

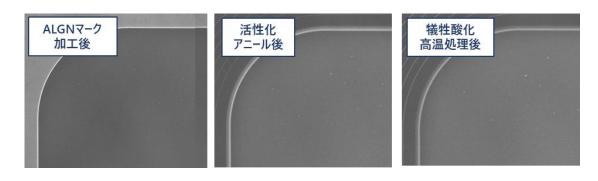

10 kV 向け高信頼ターミネーション設計を適用し、パルス電源向け 10 kV SiC PND の試作を行った。試作中、主要な工程 (高温となる工程) にて結晶欠陥を評価した結果、試作中に新たなBPD の形成はなく、良好な結晶状態であることを確認した (図 1–17)。試作した SiC PND は、プローブ評価において良好なダイオード特性を示し、順方向電流密度 100 A/cm² でオン電圧 4.3 V を示した (図 1–18 (a))。また、逆方向電圧 10 kV でリーク電流  $6 \times 10^{-8}$  A/cm² を示し、耐圧 10 kV 以上を達成した (図 1–18 (b))。

図 1-17 10 kV SiC PND 試作中の結晶状態 (PL像)

図1-18 10 kV SiC PNDの(a) 順方向特性(b) 逆方向特性

# ②SiC IGBT 通電劣化現象の解明と抑制(担当: (株)日立製作所)

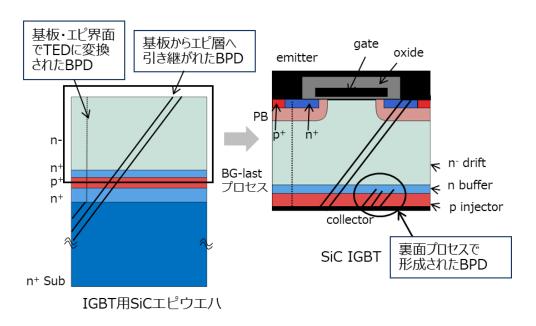

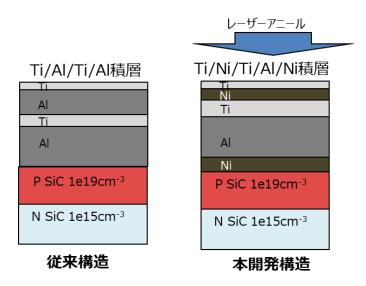

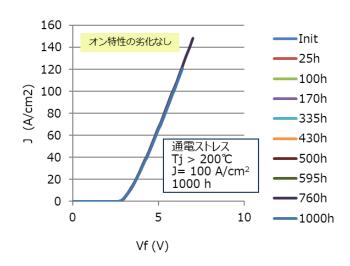

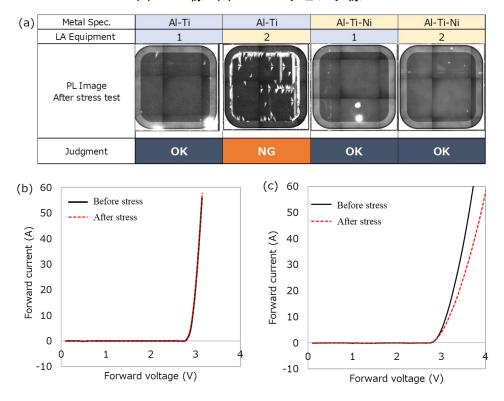

①で試作する SiC IGBT における通電劣化現象を解明し、それを抑制する作製プロセスを検討した。通電劣化現象を引き起こす基底面転位(BPD)は、裏面研削プロセスを適用する SiC IGBT では裏面プロセスでの形成が懸念される(図 2-1)。BPD の形成を抑制する裏面プロセスとして  $\text{Ti/Al/Ni}}$  積層金属+レーザーアニールプロセスを開発した(図 2-2)。開発したプロセスを適用した PiN ダイオード(PND)における通電劣化現象を解析し、開発シリサイドプロセスを適用した SiC PND は 1000 時間通電ストレス試験で特性劣化ないことを明らかにしその効果を確認した(図 2-3)。

図 2-1 SiC IGBT の裏面コンタクトプロセス中に形成される BPD

図2-2 BPDの形成を抑制する裏面プロセス

図 2-3 開発した裏面プロセスを適用した PND 通電ストレス中のオン特性

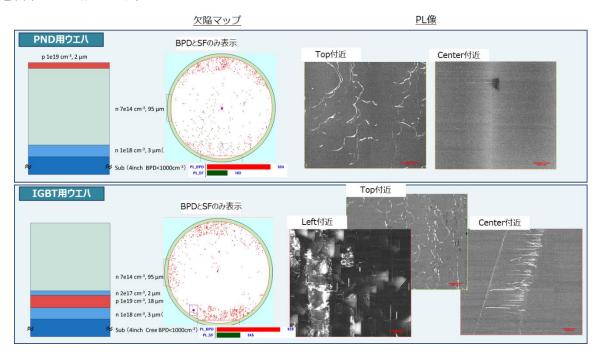

ウェハの結晶欠陥とデバイス特性の相関の解明に向け、10 kV SiC IGBT、PND 試作前の厚膜エピウェハのフォトルミネッセンス(PL)・放射光トポグラフィ評価を行ない、結晶状態を評価した(図 2-4)。

図2-4 厚膜エピウェハのフォトルミネッセンス(PL)・放射光トポグラフィ評価

実施項目①で試作する SiC IGBT における通電劣化現象を抑制するため、高信頼な IGBT 裏面プロセスについて検討した。加えて、パルス電源向け 10kV SiC PND の試作を行い、その初期評価を実施した。

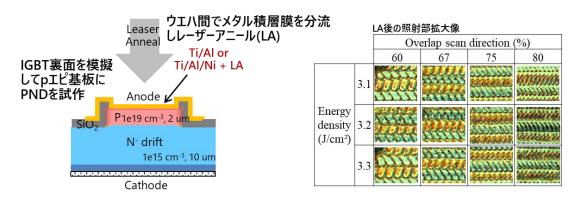

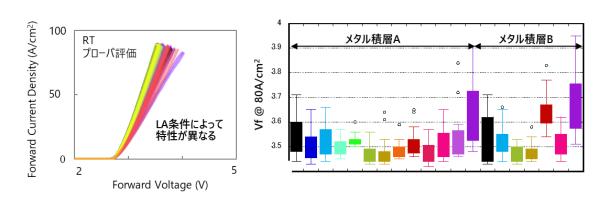

SiC IGBT の裏面電極は、ウエハ裏面を研削して金属積層膜を形成し、レーザーアニールすることで形成する。この際、通電劣化現象を引き起こす基底面転位 (BPD) の形成が懸念される (図 2-1)。これを抑制するデバイス作製プロセスを考案するため、ウエハ間で金属積層膜種を、ウエハ内でレーザーアニール条件を考案し、 IGBT 裏面を模擬した SiC PND を分流試作した (図 2-5、表 2-1)。試作した SiC PND の初期動作を確認し (図 2-6)、金属積層膜種やレーザーアニール条件に応じて電気特性が変化することを明らかにした (図 2-7)。とともに、高信頼な裏面プロセスの開発を目指す。

図 2-5 IGBT 裏面を模擬した SiC PND 試作 表 2-1 レーザーアニール後の光学顕微鏡像

図 2-6 SiC PND の順方向特性 図 2-7 SiC PND オン電圧のレーザーアニール条件依存

SiC IGBTは、図2-1に示すように、n型の4H-SiC基板の上にp+型のキャリア注入層、n+型のバッファ層、n-型のドリフト層を成膜したエピ基板を用いて製造される。ドリフト層の表面側にデバイス構造を作成し、その後、裏面のSiC基板を研削により取り除き、p+型のキャリア注入層を露出させる。続いて、金属積層膜を形成し、レーザーアニールによる裏面コンタクト形成及び電極成膜を行うことでSiC IGBTが完成する。この際、図2-1に示すように、通電劣化現象を引き起こす基底面転位(BPD: Basal Plane Dislocation)の形成が懸念される。これを抑制する、高信頼なSiC IGBT裏面コンタクト形成プロセスを開発するため、IGBT裏面を模擬したSiC PNDを試作した。

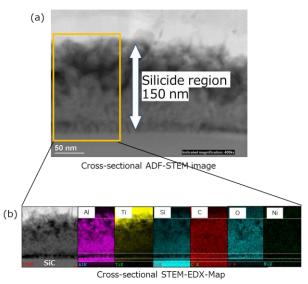

図2-5に試作したSiC PNDの断面図を示す。アノードコンタクトはp型のSiC上にAl-Tiあるいは Al-Ti-Niからなるメタル積層膜の上から、レーザーアニールすることにより形成した。レーザーアニール処理後は未反応メタルを除去し、アノード電極パッドとなるAlを成膜した。図2-8にシリサイド領域の詳細な分析結果を示す。図2-8 (a)は断面TEM(Transmission Electron Microscope)像であり、(b)は断面のEDX(Energy Dispersive X-ray Spectroscopy)マッピング像である。これから、各金属元素を含むシリサイド層は150 nm程度の厚さで形成されていることがわかる。

続いて、試作したSiC PNDに対して、通電試験を実施した。通電試験は接合温度を $175^{\circ}$ C、電流密度 $300~A/cm^2$ とし、通電時間は20時間とした。通電試験の前後で順方向電流電圧特性を測定し、オン電圧に変化がないサンプルを「0K」とし、オン電圧が増加したサンプルを「NG」と判定した。通電試験後に、表面電極構造を除去し、PLイメージング法により結晶状態を評価した。その結果をまとめて、図2-9(a)に示す。また、オン電圧が劣化しない/したサンプルの電気特性をそれぞれ図2-9(b)と(c)に示す。Al-Ti-Niのメタル積層膜では、すべてのレーザーアニール条件(装置)で通電劣化は抑制された。

以上から、AI-Ti-Niのメタル積層膜に対してレーザーアニール処理することで、通電劣化を抑制でき、高い通電信頼性を持つコンタクトを形成可能であることを実証した。

図 2-8 シリサイド領域の分析結果 (a) TEM 像 (b) EDX マッピング像

図 2-9 (a) SiC PND の通電試験結果 (b) (c) 通電試験の前後で SiC PND のオン電圧が劣化しない/したサンプルの順方向電気特性

# ③ジャスト基板を用いたエピ膜成長技術

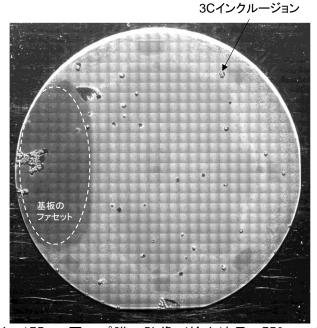

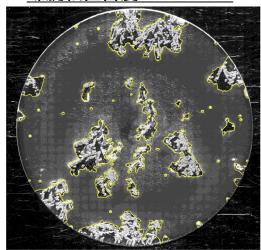

初年度の令和2年度は、ジャスト基板上のエピ成長研究を行うためのCVD装置の立ち上げ作業およびジャスト基板上のエピ成長で大きな課題となる3Cインクルージョンの発生を抑制するため、40  $\mu m$ 厚成長において基板温度、成長ガス圧力及び流量などのパラメータの最適化を試みた。その結果、成長条件による再現性なく、基板中央部の広範囲に3Cインクルージョンが発生するという課題を発見した。図3.1に、40  $\mu m$ 厚エピ膜のPL像(検出波長:750 m以上)を示す。基板中央部に楕円状に3Cインクルージョンが広がっていることが分かる。同じ条件で成長を行っても、このような3Cインクルージョンが発生するときとしないときがあることが分かった。

# 基板のファセット

図3.1 40 μm厚エピ膜のPL像(検出波長:750 nm以上)

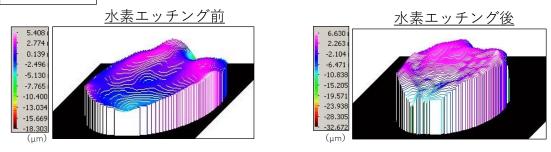

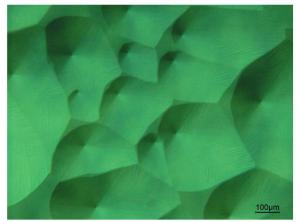

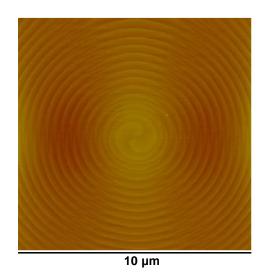

令和3年度は、基板中央部に発生する3Cインクルージョンの原因究明のため、SiC基板の水素エッチング量から基板上の温度分布を推定することを試みた。図3.2にSiC基板の水素エッチング前後の基板形状を示す。基板中央部の水素エッチング量が極端に少ないことから、基板の中央部の温度が周辺部と比較して大幅に低下していることが分かった。温度分布を改善するため部材形状の改造を行った後、SiC基板の水素エッチング量を確認した。図3.3に部材改造後におけるSiC基板の水素エッチング前後の基板形状を示す。部材改造前の図3.2と比較し、部材改造後には水素エッチング量が均一であり温度分布が改善していることが分かる。部材改造後における40 μm厚成長において、基板中央部の広範囲に発生していた3Cインクルージョンが再現性良く抑制できていることが確認できたため、175 μm厚成長を行った。図3.4に175 μm厚エピ膜のPL像(検出波長:750 nm以上)を示す。3Cインクルージョン密度は0.8/cm²であり、令和3年度の目標値である1/cm²以下を達成した。図3.5及び図3.6に175 μm厚エピ膜の光学顕微鏡像およびAFM像を示す。ジャスト基板を用いたエピ成長特有のスパイラル成長をしていることが確認できた。

# 部材改造前

#### 水素エッチング後 水素エッチング前 4.557 3.528 1.945 2.498 1.556 1.166 1.469 0.777 0.440 0.387 -0.590 -0.002 -1.619 -0.392 -2.648 -0.781 -3.677 -1.170 -4.707 $(\mu m)$

図3.2 従来部材使用時のSiC基板の水素エッチング前後の基板形状

# 部材改造後

図3.3 部材改造後のSiC基板の水素エッチング前後の基板形状

図3.4 175 µm厚エピ膜のPL像(検出波長: 750 nm以上)

図3.5 175 µm厚エピ膜の光学顕微鏡像

図3.6 175 µm厚エピ膜のAFM像

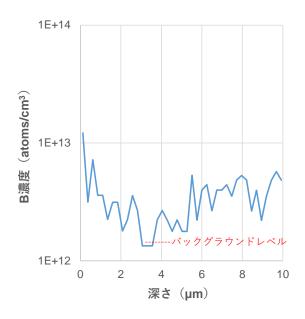

低欠陥密度の175  $\mu m$ 厚エピ膜が実現できたため、低キャリア濃度制御および高ライフタイムの実現に重要なエピ膜中のB濃度を評価した。図3.7に175  $\mu m$ 厚エピ膜のエピ表面からの深さとB濃度の関係を示す。B濃度は1E+13  $\epsilon m^{-3}$ 以下であり、10 kV以上の耐圧設計に必要であるキャリア濃度5E+14  $\epsilon m^{-3}$ 以下を十分に制御可能かつ高ライフタイムも十分に実現可能である低B濃度であることが確認できた。

図3.7 175 µm厚エピ膜のB濃度

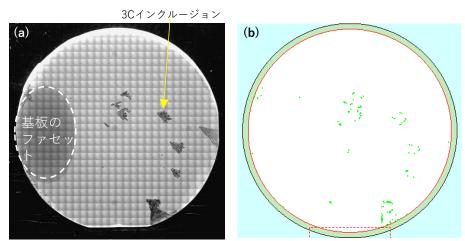

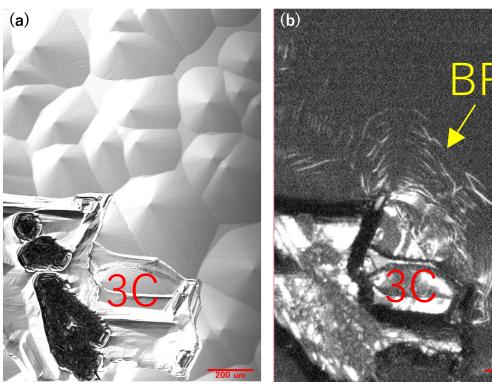

また、ジャストエピ成長は、成長方向が基底面と垂直であるため、原理的に基板の基底面転位のエピ膜中への引継ぎが無いことが利点である。基底面転位密度の評価のため、40 μm厚エピ膜のPL測定(検出波長:750 nm以上)を用いた欠陥自動検出を行った。図3.8 (a)及び (b)に40 μm厚エピ膜のPL像及び基底面転位の自動検出マップを示す。3Cインクルージョンが発生している箇所の周辺に基底面転位が検出されており、それ以外の領域では全く検出されていないことが分かる。図3.9 (a)及び (b)に3Cインクルージョンが発生している領域の光学顕微鏡像及びPL像を示す。基底面転位 (BPD)はPL像において明線として観察されるが、3Cインクルージョンの周辺に基底面転位が発生していることが確認できる。このように、3Cインクルージョン起因の基底面転位は発生してしまっているが、ジャスト基板を用いることにより、基板の基底面転位の引継ぎは抑制できていることが分かった。

図3.8 (a) 40 μm厚エピ膜のPL像(検出波長: 750 nm以上) (b) 基底面転位の検出マップ

図3.9 (a) 3Cインクルージョン発生領域の光学顕微鏡像(b) PL像(検出波長:750 nm以上)

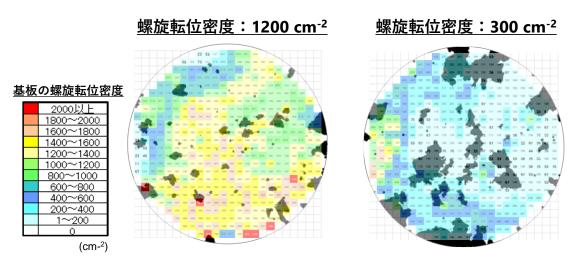

令和4年度は、30インクルージョン発生における基板の螺旋転位密度の影響を評価し た。本プロジェクト前半では、螺旋転位密度が1000 cm<sup>-2</sup>以上のジャスト基板を用いてお り、そのような基板上への175 μm厚エピ膜において前述の通り3Cインクルージョン密度 0.8/cm<sup>2</sup>を達成した。しかし、昨今、SiC基板の品質向上が進んでおり、また、ジャスト基板 を用いたエピ膜成長は基板の螺旋転位からの成長を用いるため、30インクルージョンの 発生は基板の螺旋転位密度の影響を受けると考えた。ジャスト基板の螺旋転位密度をX 線トポグラフ測定により評価し、螺旋転位の平均密度が1200 cm<sup>-2</sup>と300 cm<sup>-2</sup>の基板を準 備した。図3.10に、それぞれの基板上に170  $\mu$ m厚成長したエピ膜のPL像(検出波長: 750 nm以上)を示す。黄線で囲っている部分が3Cインクルージョンである。3Cインクル ージョンのウェハ全面に対する面積割合は螺旋転位密度が1200 cm<sup>-2</sup>のときは8%、螺旋 転位密度が300 cm<sup>-2</sup>のときは22%であり、基板の螺旋転位密度が低い基板上への成長で は30インクルージョンの面積割合が増加していることが分かる。図3.11に、基板の螺旋 転位密度分布マップとエピ膜の3Cインクルージョン領域を黒色としたマップを重ね合 わせたものを示している。これを見ると、螺旋転位の平均密度が300 cm<sup>-2</sup>基板上に成長 したエピ膜について、螺旋転位密度が400 cm<sup>-2</sup>以下の領域に30インクルージョンが広が っていることが分かる。螺旋転位密度が低いときには、螺旋転位から発生するスパイラ ル成長で成長表面が覆われるまでの時間が長くなり、基板の有する広いテラス上への3C 核発生が増加すると考えられる。このように、ジャスト基板の螺旋転位密度と3Cインク ルージョン発生との関係を発見し、30インクルージョン発生への影響の大きい螺旋転位 密度を明確化した。

# 螺旋転位密度:1200 cm-2

# PL(>750 nm)

# 螺旋転位密度:300 cm-2

図3.10 螺旋転位密度の異なる基板上に成長した170 μm厚エピ膜のPL像 (検出波長: 750 nm以上)

図3.11 基板の螺旋転位分布マップとエピ膜の30インクルージョンマップの重ね合わせ

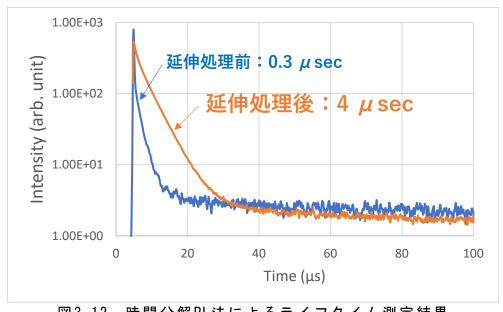

ライフタイムについては、ライフタイムを低下させることが報告されているB以外の不純物であるAI、V、TiについてもSIMS測定を行い、これらの元素の取り込みが検出限界以下であることが確認した。そこで、窒素流量を調整することによりキャリア濃度  $4.9E+14~cm^{-3}$ の  $170~\mu$  m厚ジャストエピ膜を成長し、平坦化加工後(加工後厚さ: $130~\mu$ m)にライフタイム測定を行った。図3.12に時間分解PL法によるライフタイム測定結果を示す。ライフタイム 延伸処理である C注入を行っており、延伸処理前を青色、延伸処理後を橙色で示している。延伸処理前のライフタイム(Log (1/e)-Log  $(1/e^2)$  で導出)は $0.3~\mu$  sec、延伸処理後のライフタイムは4 $\mu$  secであり、延伸処理によりライフタイムが大幅に増加していることが分かる。ライフタイム延伸処理である C注入は、ライフタイムを低下させるで発入を減少させる処理であり、上述した B等のライフタイムを低下させる不純物濃度が高いと延伸処理を行ってもライフタイムは増加しないと考えられる。今回、ライフタイムを低下させる不純物を低濃度に制御できているため、延伸処理によりライフタイムが増加しており、延伸処理後のライフタイムは最終目標の $2~\mu$  secを達成した。

図3.12 時間分解PL法によるライフタイム測定結果

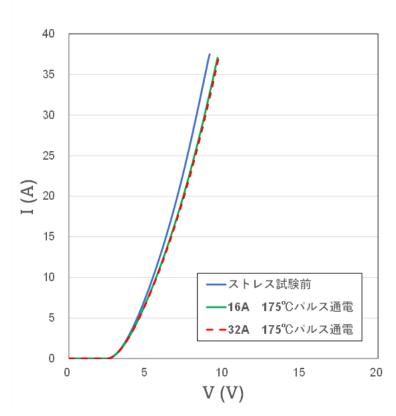

また、基底面転位のエピ膜中への引継ぎが無いために順方向劣化を抑制可能であるという利点の効果を検証するため、厚膜ジャストエピ膜の3Cインクルージョンを含まない領域を使用してPiNダイオードを作製し、順方向特性ストレス評価を行った。エピ膜のキャリア濃度は $4.9E+14~cm^{-3}$ であり、膜厚は $170~\mu$ m厚のエピ膜をデバイス作製のための表面平坦化加工を行い $130~\mu$ m厚となった。デバイス作製前にライフタイム伸長処理を行った。電極サイズは4~mm角とした。順方向ストレス試験は、パルス幅 $50~\mu$ sec、周波数1~kHzで4時間行った。温度は175~cで、電流値は16~A(電流密度:約 $105~A/cm^2$ )及び32~A(電流密度:約 $209~A/cm^2$ )とした。図3.13にストレス試験前後の1V特性を示す。ストレス試験前後で電流値はほぼ変化していないことが分かる。基板の基底面転位の引継ぎが無く、順方向劣化が抑制されたと考えられる。デバイス作製によりジャストエピ成長の効果を検証することができた。

図3.13 ストレス試験前後のIV特性

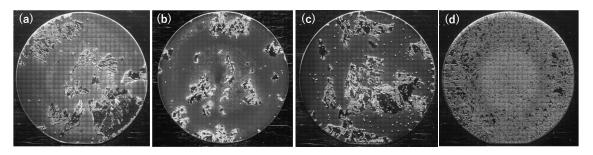

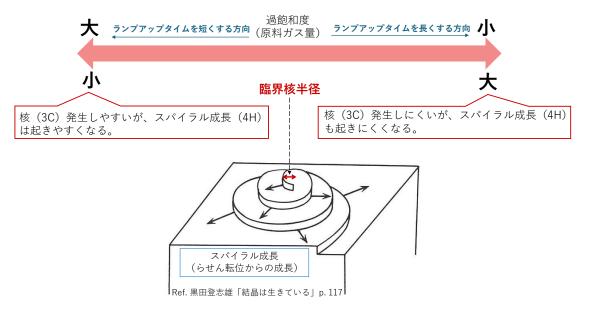

最終年度の令和5年度は、平均螺旋転位密度400 cm<sup>-2</sup>以下の基板上への成長において30インク ルージョンを抑制するため、成長初期条件の見直しを行った。具体的には、原料ガスをマスフロ ーコントローラの最小流量から到達流量に増加させるまでの時間(ランプアップ時間)との関係 を評価した。令和4年度までの成長における標準的なランプアップ時間は1時間としていた。図3.14 にランプアップ時間を(a) 40分、(b) 1時間、(c) 2時間、(d) 3時間と変化させたときの150  $\mu$  m厚成長したエピ膜のPL像(検出波長:750 nm以上)を示す。これを見ると、これま での標準的なランプアップ時間である1時間で成長したエピ膜において30インクルージ ョンの発生が最も抑制できており、ランプアップ時間を1時間から長くしても短くして も30インクルージョンは増加傾向にあることが分かった。この現象についての考察を図 3. 15のスパイラル成長の概略図を用いて説明する。ランプアップ時間を長くするという ことは、成長初期の過飽和度を低下させるということだが、過飽和度が低下すると臨界 核半径が大きくなる。すなわち、核発生は起きにくくなるため、SiCエピ成長温度にお いて安定である3C-SiCの核が発生しにくくなる。しかし、臨界核半径が大きくなるとス パイラル成長が進むのが遅くなるため、基板表面が4H-SiCのスパイラル成長で覆われる までの時間が長くなると考えられる。一方、ランプアップ時間を短くすると成長初期の 過飽和度が増加するので臨界角半径が小さくなる。すなわち、3C-SiCの核発生が起きや すくなるが、スパイラル成長も早く進むため、基板表面が4H-SiCのスパイラル成長で覆 われるまでの時間が短くなると考えられる。このように、3C-SiCの核抑制と4H-SiCのス パイラル成長促進はトレードオフの関係にあり、3Cインクルージョン抑制のためのラン プアップ時間の最適値があることが分かった。

図3.14 ランプアップ時間を変化させて成長した150  $\mu$  m厚エピ膜のPL像 (検出波長: 750 nm以上) (ランプアップ時間: (a) 40分、(b) 1時間、(c) 2時間、(d) 3時間)

図3.15 スパイラル成長の概略図

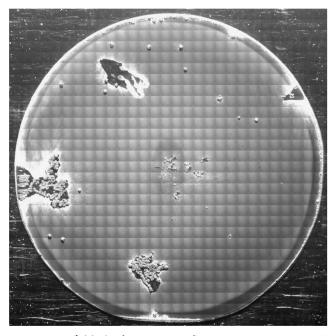

ランプアップ時間を変化させても3Cインクルージョンの抑制は実現できなかったため、成長に使用する炭素部材のコーティング材の変更を行った。図3.16に、炭素部材のコーティング材を変更して成長した $150~\mu$ m厚エピ膜のPL像(検出波長:750~nm以上)を示す。本成長に用いたジャスト基板の平均螺旋転位密度は340~cm²である。炭素部材のコーティング材変更前においては、低螺旋転位密度のジャスト基板上のエピ膜で3Cインクルージョンが最も抑制されたのは、図3.10の右図及び図3.14(b)のPL像に示すものである。このときの3Cインクルージョンのウェハ全面に対する面積割合は22%であった。それに対したの3.16に示す炭素部材のコーティング材変更後のエピ膜の3Cインクルージョンのウェハ全面に対する面積割合は4%であり、3Cインクルージョンの面積割合が大幅に低減した。3Cインクルージョン密度としては0.8~cm²であり、最終目標である0.2~cm²には至らなかったが、SiC基板の品質向上に伴う3Cインクルージョンの面積割合の低減の要因にな課題を発見し、その低減に成功した。3Cインクルージョンの面積割合の低減の要因にないては今後の検討が必要だが、炭素部材のコーティング材を変更することにより成長中のガス雰囲気が変化したため、スパイラル成長の進行が促進したと推定している。

図3.16 炭素部材のコーティング材を変更して成長した150  $\mu$  m厚エピ膜のPL像 (検出波長:750 nm以上)

ライフタイムについては、令和4年度に、延伸処理後のエピ膜において4  $\mu$  secを達成したので、その要因を評価するため、170  $\mu$  m厚エピ膜のライフタイム延伸処理前後のDLTS測定を行った。表3.1に延伸処理前、表3.2に延伸処理後のDLTS測定結果を示す。延伸処理前には、ライフタイムを低下させることが知られているZ1/2センターが3.9E+14 cm<sup>-3</sup>という高密度で検出されているが、ライフタイム延伸処理後には検出されなかった。ライフタイム延伸処理であるC注入により、Z1/2センターの起因である炭素空孔が十分に減少していることが確認できた。この結果から、ジャストエピ膜においても、通常の4度オフエピ膜で用いられているライフタイム延伸処理が適用可能であり、十分に長いライフタイムを実現できることが分かった。

表3.1 延伸処理前のDLTS測定結果

| 活性化エネルギー<br>(eV) | 捕獲断面積<br>(cm²) | トラップ密度<br>(cm <sup>-3</sup> ) | 起源<br>(推定) |

|------------------|----------------|-------------------------------|------------|

| 0.15             | 1E-15          | 5.8E+12                       | Ti         |

| 0.67             | 7E-15          | 3.9E+14                       | Z1/2       |

| 1.57             | 6E-15          | 2.8E+14                       | EH6/7      |

表3.2 延伸処理後のDLTS測定結果

| 活性化エネルギー<br>(eV) | 捕獲断面積<br>(cm²) | トラップ密度<br>(cm <sup>-3</sup> ) | 起源<br>(推定) |

|------------------|----------------|-------------------------------|------------|

| 0.15             | 5E-16          | 9.9E+11                       | Ti         |

| 0.67             | -              | -                             | Z1/2       |

| 1.12             | 6e-15          | 4.5e+13                       | EH6/7      |

# ④SiCサイリスタによるエピ膜品質評価

エピ膜品質を評価するためのSiCサイリスタの構造設計を実施した。図4.1に、本事業で開発するSiC-GTOサイリスタの基本構造図を示す。pnpnの基本サイリスタ構造に加え、ターンオフを実現するためのゲート電極、電流の出入り口となるアノード、カソード電極から構成される。ここでは、耐圧を維持するためのドリフト層がn型の構造を採用した。

図4.1 SiC-n型GTOサイリスタの断面構造図

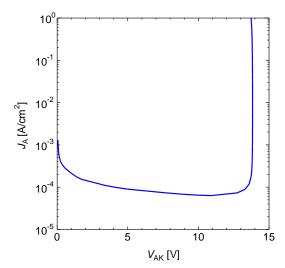

図4.2にTCADシミュレータ(Synopsis社製Sentaurus)を用いて計算したSiC-n型GTOサイリスタのオフ時の電流・電圧特性を示す。定格耐圧10 kVに対して+20%程度の設計マージンを加えることを設計指針としたが、それを超える13 kV強のブレークダウン電圧の計算結果が得られた。

図4.2 SiC-n型GTOサイリスタのオフ特性

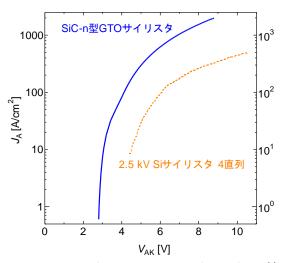

また、図4.3に同素子のオン時の電流・電圧特性のシミュレーション結果を示す。電流密度100 A/cm² においてオン電圧4.1 Vという値が得られ、これは耐圧2.5 kVのSiサイリスタ (東芝製 SF1500EX24)を4直列にし、今回設計したSiC-GT0サイリスタと同じ耐圧にした場合と比較しても大幅なオン電圧低減効果(6.1 V  $\rightarrow$  4.1 V)が得られており、10 kVを超える高耐圧レンジにおいてSiに対するSiCの優位性を示すことができた。

図4.3 SiC-n型GTOサイリスタのオン特性

次に、SiGサイリスタのマスク設計を行うとともに、デバイス試作するためのプロセス工程を策定した。既に産総研、及び電中研が有するBPD密度を低減する技術を活用したエピウェハを作製し、上記プロセス工程に従ってSiGサイリスタを作製した。作製したSiGサイリスタの耐電圧特性や通電特性、スイッチング特性などの電気特性を評価した。

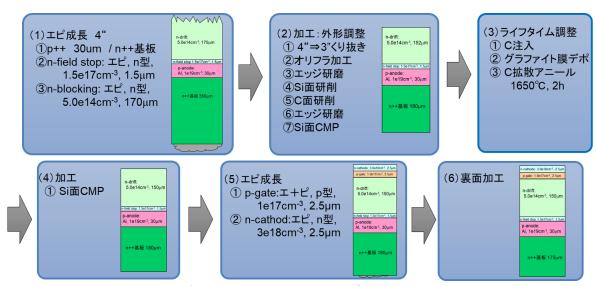

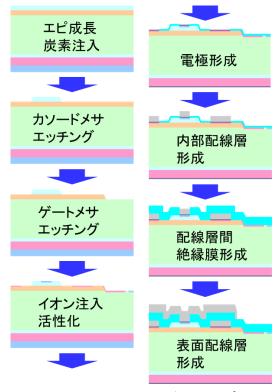

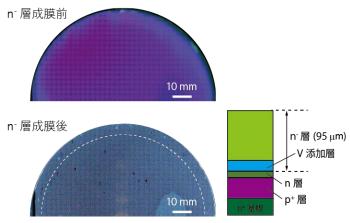

10 kVを超える超高耐圧デバイスを作成するためには100 µmを超える厚みのエピタキシャル膜が必要になるが、ウェハ表・裏面のモフォロジー劣化、ウェハエッジ部の欠陥発生など、多くの問題が発生する。本研究ではそれらの課題を解決するために、厚膜エピ成長後、ウェハ加工技術を駆使してデバイス試作に供し得る厚膜エピウェハを準備した。ウェハ加工工程を図4.4に示す。

図4.4 デバイス試作用SiC厚膜エピウェハの加工工程

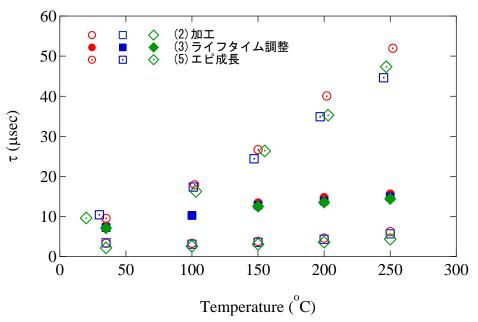

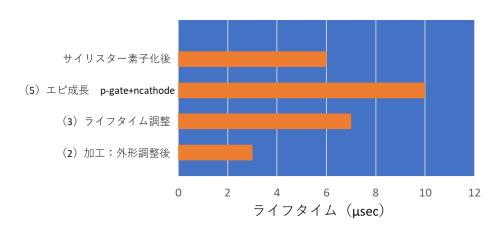

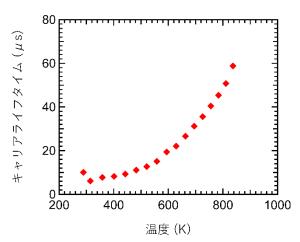

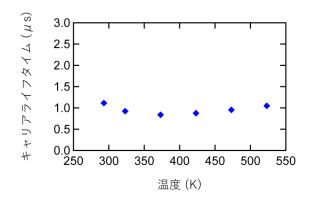

SiCバイポーラデバイスの電流電圧特性に大きな影響を及ぼす少数キャリアライフタイムの評価を、上記加工工程を経た厚膜エピウェハについて行った。図4.4のウエハ加工工程の(2)、(3)、(5)の状態でのライフタイムの温度依存性を3インチ面内の平均値としてプロットした結果を図4.5として示す。ライフタイムの温度依存性評価は差動 $\mu$ 波PCD装置を用いて行った。図4.4の加工工程(2)の状態は材料特性としては成長直後(as-grown状態)と同じであるがこの時に室温で約3 $\mu$ sec、250°Cでは5.3 $\mu$ secとas-grown状態では比較的長いライフタイムが得られている。これらのウエハにキャリアライフタイム改善のために、炭素原子の高温拡散によるキャリアトラップのパッシベーション技術を活用した結果(図4.4(3)工程)室温で約7 $\mu$ sec、250°Cで約15 $\mu$ secとキャリアトラップ低減の効果が出ているこ

とを確認した。この状態からさらにP-gate層並びにn-cathod層をエピ成長(図4.4(5) 工程)させてもライフタイムの低下は見られず、室温で約 $10\mu$  sec、 $250^{\circ}$ Cでは約 $48\mu$  secむしろ増加した。これは n ドリフト層とp-gate層の接合によりライフタイムにおける表面再結合速度の影響が低減し、測定されるライフタイムが向上したものと考えられる。

図4.5 ライフタイムの温度依存性

さらに図4.6にサイリスタ素子試作後に測定したライフタイムも含めてウェハ作製から素子試作工程まで含めた室温でのライフタイムの推移をしめす。素子化後のライフタイムとしては約 $6\mu$  secであり、ライフタイム調整後(図4.4(3))の値に戻っていることが判る。このことから素子化のプロセスは基本的には材料レベルで改善したライフタイムには影響を与えていないと考えられる。

図4.6 各工程でのライフタイムの推移

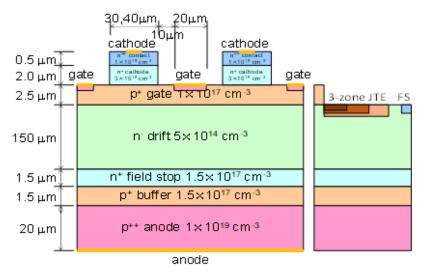

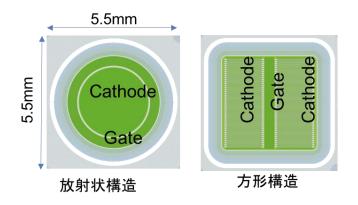

SiCサイリスタの構造設計、及びデバイスプロセスについて具体的に述べる。ここでは、アバランシェ耐圧を14 kVとして設計した。素子の断面構造を図4.7に示す。カソード層をメサ構造とすることでゲート領域を形成し、更に終端構造として3段階JTE (Junction Termination Extensioin)構造を採用するため、ゲート層もメサ構造とした。また電極構造として放射状ゲート構造と方形構造を採用し、電気特性の比較を行えるように設計した(図4.8)。

図4.7 SiCサイリスタ素子断面構造

図4.8 SiCサイリスタ電極構造

上記デバイスを作成するためのデバイスプロセスを図4.9に示す。

図4.9 SiCサイリスタのデバイスプロセス

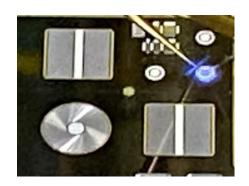

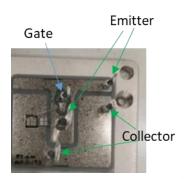

図4.10に同デバイスプロセスにより試作したSiCサイリスタの外観を示す。

図4.10 試作したSiCサイリスタの写真

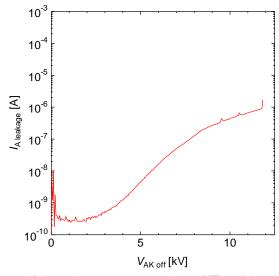

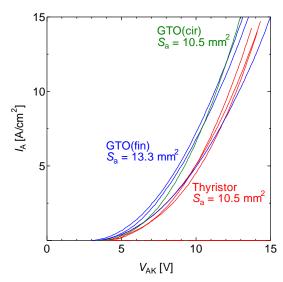

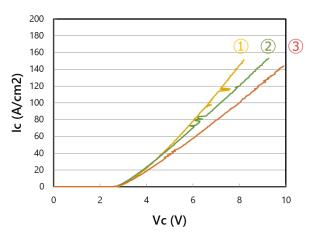

図4.11に試作したSiCサイリスタの耐電圧(オフ)特性を示す。耐電圧値として11.8kVが得られた。この値は理論耐圧の約84%となる。図4.12に試作したSiCサイリスタの通電(オン)特性を示す。オン電圧は、 $10A/cm^2$ で $11\sim14V$ と高くなった。ライフタイムを伸長したエピウェハを用いたバイポーラデバイスとしては、大きめの値となった。

図4.11 試作したSiCサイリスタの耐電圧(オフ)特性

図4.12 試作したサイリスタの通電(オン)特性

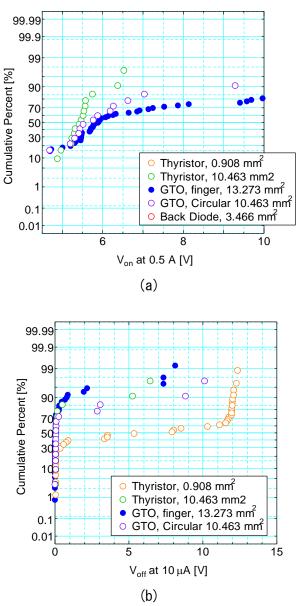

試作したサイリスタのオン電圧と耐電圧の代表的な累積確率プロットを図4.13に示す。オン電圧の中央値は5.8Vとなった。ライフタイムを伸長したエピウェハを用いたバイポーラデバイスとしては、大きめの値となっており、引き続き検証を行う。耐電圧値が12kV以上となる素子が30%以上得られた。12kVは理論耐圧の85%である。

図 4.13 試作したサイリスタの(a)オン電圧と(b)耐電圧の代表的な累積確率プロット

# ⑤大電流パルス動作時におけるキャリア再結合のモデル化とキャリアライフタイム制御(担当: (一財)電力中央研究所)

SiC-IGBT は、耐圧を維持するための n 型層および少数キャリアを注入する p 型層の積層構造からなる。 IGBT はエミッタ・コレクタからのキャリア注入によりオン状態の抵抗を低下させるが、一方でターンオフ時には注入したキャリアを消滅もしくは掃き出す必要がある。オン電圧の低減には、n 型層のキャリアライフタイムを延伸させることが有効となるが、低オン電圧と高速スイッチングにはトレードオフ関係が存在する。トレードオフ関係の緩和にはキャリアプロファイルを最適化するための設計技術とキャリア寿命制御技術が求められる。このため、1 kA/cm²以上までの SiC-IGBT の大電流動作を想定し、n 型層(耐圧維持層)および p 型層(コレクタ層)のキャリア再結合モデルを構築するとともに、局所キャリアライフタイム制御技術の開発を行い、以下の成果を得た。

# 5.1 キャリア再結合のモデル化

n 型および p 型 SiC 単結晶膜のキャリア再結合モデルの構築に向けて、ドーピング密度の異なる SiC エピ膜を作製し、時間分解フォトルミネッセンス(TRPL)測定によりキャリアライフタイムの温度依存性を評価した。

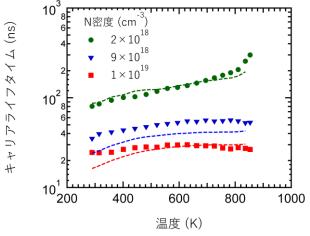

SiC-IGBT の耐圧維持層を想定し、炭素拡散処理によるキャリアライフタイム延伸処理を施した窒素 (N) ドープ n 型エピ膜(N 密度:  $1\times10^{15}$  cm<sup>-3</sup>、膜厚:  $120~\mu m$ )の温度範囲 290-840~K におけるキャリアライフタイムを評価した(図 5.1)。測定温度の上昇に伴い、キャリアライフタイムは単調に増大した。この結果は、低ドーピング密度 n 型 ( $n^-$ ) 層のキャリア再結合が Shock ley-Read-Hall (SRH) 過程によって支配的に決められており、高温になるにつれて、炭素空孔による  $Z_{1/2}$  センター ( $E_c$ -0.63~eV) などの再結合中心を介した SRH 再結合過程の寄与が低下し、キャリア寿命が増大したものとして理解できる。

次に、N密度 2×10<sup>18</sup>. 9×10<sup>18</sup>. 1×10<sup>19</sup> cm<sup>-3</sup> の高ドーピング密度 n 型(n<sup>+</sup>)層のキャリアラ イフタイムの温度依存性を評価した(図5.2)。 N 密度 2×10<sup>18</sup> cm<sup>-3</sup>の試料においては温度上昇 に伴ってキャリアライフタイムが増大する傾 向が認められたが、N密度の増加に伴ってキャ リアライフタイムの温度依存性が弱まること が確認された。N 密度 1×10<sup>19</sup> cm<sup>-3</sup>の試料のキ ャリアライフタイムは、300-840 Kの温度範囲 において 25-30 ns であった。キャリア再結合 における直接再結合過程と Auger 再結合過程の 寄与は、自由キャリア密度が高くなるにつれて 大きくなり、n<sup>+</sup>層においては直接再結合過程と Auger 再結合過程が主要な再結合過程になる [1]。N 密度 1×10<sup>19</sup> cm<sup>-3</sup> のイオン化率は 300-840 Kにて 0.3-0.9 であり、温度上昇に伴って イオン化率が高まることで、直接再結合と Auger 再結合の寄与が増大し、キャリアライフ

図 5.1 キャリアライフタイム延伸処理を行った n エピ膜 (N 密度  $1 \times 10^{15}$  cm  $^{-3}$ 、膜厚 120  $\mu$ m) のキャリアライフタイムの温度依存性の測定結果

タイムが低下すると考えられる。しかし、実験的に観測されたキャリアライフタイムの 300-840 K における変化割合は 20%以下と小さく、イオン化率の変化だけでは測定されたキャリアライフタイムの温度依存性を説明できない。そこで、式(1)により N ドナー準位を介したキャリア再結合過程を考慮してモデル式解析を実施した。

$$\frac{1}{\tau} = A + Bn + C_n n^2 + B_N N_{uN} + C_N N_{uN}^2$$

(1)

図 5.2 N ドープ  $n^+$ エピ膜 (N 密度  $2 \times 10^{18}$ , 9  $\times 10^{18}$ ,  $1 \times 10^{19}$  cm<sup>-3</sup>) のキャリアライフタイムの温度依存性の測定結果 (シンボル) とモデル式による計算結果 (点線)

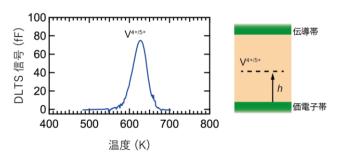

図 5.3 V ドープ p 型エピ膜の DLTS スペクトル

ここで、 $\tau$  はキャリアライフタイム、A は SRH 再結合係数、B は直接再結合係数、 $C_n$  は Auger 再結合係数、 $B_N$  および $C_N$ は N ドナー準位を介したキャリア再結合の再結合係数、 $N_{uN}$  は非イオン化 N ドナー密度である。Bを  $1 \times 10^{-12}$  cm³/s、 $C_n$ を  $2 \times 10^{-31}$  cm6/s [2,3] として、 $B_N$ を  $1 \times 10^{-12}$  cm³/s、 $C_N$  を  $6 \times 10^{-31}$  cm6/s とした場合に、N ドープ n<sup>+</sup>層のキャリアライフタイムの測定結果とモデル式による計算結果が概ね一致することを確認した(図 5.2)。

ギー準位と  $V^{4+/5+}$ エネルギー準位の差は、ESR 測定から求められた値と一致することから [7]、本信号は  $V^{4+/5+}$ 準位に起因していると判断される。

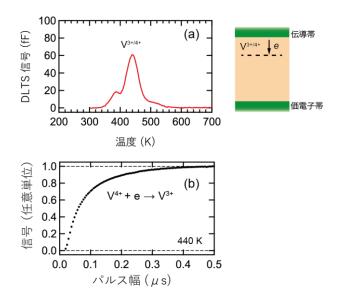

次に、パルスフィリング法を用いて、V<sup>3+/4+</sup> アクセプター準位および V4+/5+ドナー準位の捕 獲断面積を評価した。図 5.4(a)に V ドープ n 型層の DLTS スペクトルを示す。 温度 420 K に ピークを有する V<sup>3+/4+</sup>準位に対応する信号が観 測されている[4.5]。温度を 440 K 一定に保 ち、パルス幅を変化させながら DLTS 測定を行 った結果を図 5.4(b)に示す。パルス幅を変え ることでトラップ準位のキャリア捕獲率(占 有率)が変化し、パルス幅が長くなるにつれ て DLTS 信号強度が大きくなっている。この信 号強度のパルス幅依存性から、室温における V<sup>3+/4+</sup>準位の電子に対する捕獲断面積が 9×10<sup>-</sup> <sup>15</sup> cm<sup>2</sup>と求まった。p 型の V ドープ層に対して も同様の測定を実施し、室温における V4+/5+準 位の正孔に対する捕獲断面積が2×10<sup>-21</sup> cm<sup>2</sup>と 求まった。キャリア再結合のモデル化には多 数キャリアの捕獲過程の捕獲断面積に加え て、少数キャリアの再結合過程における捕獲 断面積の評価が必要となる。そこで、Vドープ n型 SiC エピ膜からなる PiN ダイオードに対 して DLTS 測定を行い、少数キャリア注入下に おけるキャリアの捕獲過程を調べたところ、 V<sup>3+/4+</sup>準位については、多数キャリアの捕獲過 程に比べて少数キャリアの再結合過程の捕獲 断面積が大きいことを示す結果を得た。V4+/5+ 準位の正孔に対する捕獲断面積に比べて V3+/4+ 準位の電子に対する捕獲断面積が大きく、 V<sup>3+/4+</sup>準位の正孔に対する捕獲断面積が V<sup>3+/4+</sup>準 位の電子に対する捕獲断面積より大きいこと から、V<sup>3+/4+</sup>トラップ準位を介したキャリア捕 獲・再結合過程が支配的であると考えられる。

図 5.4 (a) V ドープ n 型エピ膜の DLTS スペクトルおよび (b)  $V^{3+/4+}$ 準位の電子に対するキャリア捕獲断面積の測定結果

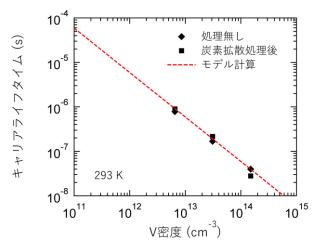

図 5.5 V ドープ n 型層のキャリアライフタイムの V 密度依存性の測定結果(シンボル) とモデル式による計算結果(点線)

このため、式(2)のモデル式を用いて、 $V^{3+/4+}$ 準位の過剰キャリア(電子)に対する捕獲断面積を $9\times 10^{-15}~{\rm cm}^2$ としてモデル計算を行った。

$$\frac{1}{\tau} = \sigma_e^{3+/4+} v_e N_V \tag{2}$$

ここで、 $\tau$ はキャリアライフタイム、 $\sigma_e^{3+/4+}$ は電子に対する  $V^{3+/4+}$ 準位の捕獲断面積、 $v_e$  は電子の熱速度、 $N_V$  は V 密度である。その結果、室温における V ドープ n 型層(V 密度: $7\times 10^{12}$  –  $2\times 10^{14}$  cm<sup>-3</sup>)のキャリアライフタイムの測定結果とモデル式による計算結果が良く一致することが確認された(図 5.5)。

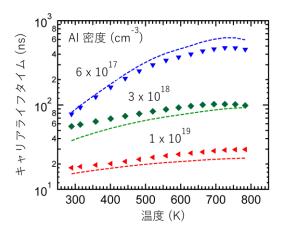

本研究課題において、SiC-IGBT のコレクタ層は AI 添加 p 型層により構成している。このため、 AI 密度の異なる SiC エピタキシャル試料(AI 密度:  $6 \times 10^{17}$  -  $1 \times 10^{19}$  cm<sup>-3</sup>)を作製し、TRPL 測定により室温から 780 K までの温度におけるキャリアライフタイムを評価した。その結果、AI 密度の増加に伴って、キャリアライフタイムが低下するとともに、キャリアライフタイムの温度依存性が弱まることが確認された(図 5.6)。AI 密度  $1 \times 10^{19}$  cm<sup>-3</sup>の試料の温度 290、780 K におけるキャリアライフタイムは 18、30 ns であり、温度上昇に伴ってキャリアライフタイムが長くなった。AI ドープ p 型層におけるキャリア再結合過程については、直接再結合過程と Auger 再結合過

程に加えて、AI アクセプター準位を介したキャリア再結合過程を考慮する必要がある[8]。そこで、式(3) において直接再結合係数Bを  $2 \times 10^{-12}$  cm $^3$ /s、Auger 再結合係数 $C_p$ を  $2 \times 10^{-31}$  cm $^6$ /s[2]として、キャリアライフタイムの AI 密度依存性の測定結果とのフィティングを行うことで、AI アクセプター準位を介した再結合過程の再結合係数 $B_{Al}$ を  $6 \times 10^{-12}$  cm $^3$ /s と求めた。

$$\frac{1}{\tau} = A + Bp + C_p p^2 + B_{Al} N_{uA}$$

(3)

ここで、p は自由正孔密度、 $N_{uA}$  は非イオン化 Al アクセプター密度である。本モデルを用いてキャリアライフタイムを計算した結果を図 5.6 に点線で示す。モデル計算結果が、実験で得られたキャリアライフタイムの Al 密度依存性および温度依存性と良く一致することが確認された。

上記で得られたキャリア再結合パラメータを用いたキャリア再結合モデルを適用することで、

図 5.6 AI ドープ p 型エピ膜のキャリア ライフタイムの温度依存性の測定結果 (シンボル) とモデル式による計算結果 (点線)

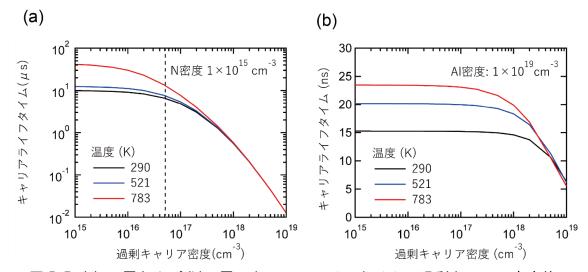

SiC-IGBT を構成する  $n^-$ 層(N 密度:  $1\times 10^{15}$  cm<sup>-3</sup>)および  $p^+$ 層(Al 密度:  $1\times 10^{19}$  cm<sup>-3</sup>)中のキャリアライフタイムの過剰キャリア密度依存性の計算結果を得た(図 5.7)。PiN ダイオードのデバイスシミュレーション結果より、電流密度 1 kA/cm² における過剰キャリア密度は  $5\times 10^{16}$  cm<sup>-3</sup>程度になると想定される。 $n^-$ 層においては大電流動作時には直接再結合および Auger 再結合の寄与が増大することにより、キャリアライフタイムが短くなるとともに、キャリアライフタイムの温度依存性が弱まることが予想される。

図 5.7 (a) n-層および(b) p-層のキャリアライフタイムの過剰キャリア密度依存性のモデル計算結果((a)中の点線は、デバイスシミュレーションにより推定した電流密度 1  $kA/cm^2$  における過剰キャリア密度の目安を示す)

# 5.2 局所キャリアライフタイム制御

キャリアライフタイムの局所的な制御方法として、プロトンなどの高エネルギー粒子線照射またはエピタキシャル成長中の不純物ドーピングがあり、両手法の制御性についての検討を実施した。

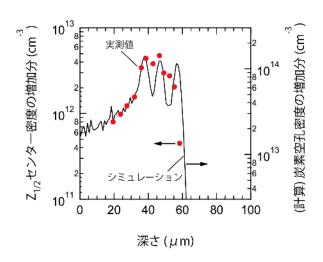

n型 SiC エピ膜に対してサイクロトロン装置を用いて、飛程 40、50、60  $\mu$ m でのプロトン照射 (照射量:  $1 \times 10^{10}$  cm<sup>-2</sup>) を行い、DLTS 法を用いて深さ方向の欠陥密度分布を評価した。プロトン 照射後の  $Z_{1/2}$  センター (炭素空孔) 密度の増加分は、プロトンの飛程に対応する深さにおいて最

大 $^{\sim}4\times10^{12}$  cm $^{-3}$ 、表面近傍において  $10^{11}$  cm $^{-3}$  台後半であった(図 5.8)。この  $Z_{1/2}$  センターの深さ方向密度分布の評価結果は、照射条件を模擬したモンテカルロシミュレーションにより推定される炭素空孔の分布と概ね一致することが確認された。

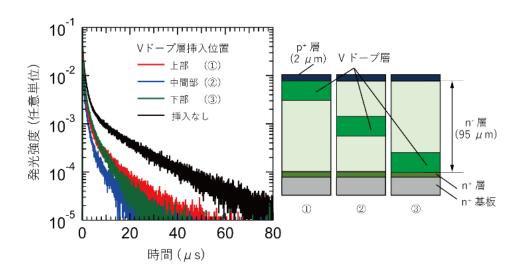

次にエピタキシャル成長中の不純物ドーピングによる局所キャリアライフタイム制御の効果を検証するために、Vを局所的(V密度:  $1\times10^{13}$  cm $^{-3}$ 、厚さ方向幅:  $20~\mu$ m)にドーピングした膜厚 95 $\mu$ mのn型SiCエピ膜を3種作製した(図5.9挿入図)。試料①は $\pi$ ドリフト層の上部、試料②は中央部、試料③は下部にVドープ層を形成した。TRPL測定によりSiCバンド端発光の減衰曲線を評価したところ、Vドープ層の挿入の有無と挿入位置に依存する結果が得られ、Vドープ層を局所的にドープすることでキャリアライフタイムを制御できることが確認された(図5.9)。

図 5.8 プロトン照射後の Z<sub>1/2</sub> センター 密度の測定結果と、プロトン照射による炭素空孔の生成密度の計算結果

図 5.9 バナジウムを局所的にドープした SiC エピ膜のバンド端発光の時間減衰特性(室温)

# 5.3 キャリアライフタイムを制御した SiC エピ膜の作製

研究テーマ①SiC エピ積層構造・ライフタイム制御と高速スイッチングSiC IGBTデバイス設計への適用手法の確立(担当:株式会社日立製作所)および研究テーマ②SiC IGBT通電劣化現象の解明と抑制(担当:株式会社日立製作所)に用いるSiCエピ膜の作製を実施した。

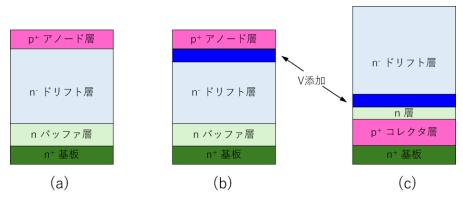

通電劣化現象の解明を目的として、バッファ層のドーピング密度(キャリアライフタイム)と膜厚をパラメータとして変化させたPiNダイオードを試作するためのエピ膜を作製した(図 5.10(a))。不純物ドーピングによる局所ライフタイム制御の効果検証を目的として、ドリフト層のキャリアライフライムをVドーピングにより局所的に変化させたPiNダイオードを試作するためのエピ膜を作製した(図5.10(b))。デバイス試作用エピ膜と同条件で成膜したVドープエピ膜(膜厚30  $\mu$ m)のキャリアライフタイムは、TRPL測定により室温から523 Kの温度範囲において約1  $\mu$ s と求まった(図5.11)。

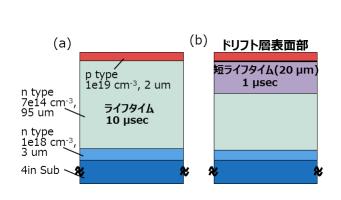

次に、ドリフト層のキャリアライフライムをVドーピングにより局所的に変化させたIGBTを試作するためのエピ膜を作製した(図5.10(c))。図5.12に作製したSiCエピ膜のフォトルミネッセンスイメージング像を示す。n-層成膜後のサンプルの三角欠陥密度は $\sim$ 0.2 cm-2であり、デバイス試作に適用できるレベルの欠陥密度を有するエピ膜を作製できたことを確認した。

図 5.10 (a) バッファ層のキャリアライフタイムを制御した PiN ダイオード、(b) 耐圧維持層のキャリアライフタイムを局所的に制御した PiN ダイオード、(c) 耐圧維持層のキャリアライフタイムを制御した IGBT の試作に供した SiC エピ膜の模式図

図 5.11 V ドープ SiC エピ膜のキャリア ライフタイムの評価結果

図 5.12 IGBT 試作用エピ膜の断面模式図とフォトルミネッセンスイメージング像 (外周より 6 mm を除いた点線領域内における三角欠陥密度:  $\sim 0.2$  cm<sup>-2</sup>)

#### 参考文献

- [1] T. Tawara, T. Miyazawa, M. Ryo, M. Miyazato, T. Fujimoto, K. Takenaka, S. Matsunaga, M. Miyajima, A. Otsuki, Y. Yonezawa, T. Kato, H. Okumura, T. Kimoto and H. Tsuchida, J. Appl. Phys. 120 115101 (2016).

- [2] A. Galeckas, J. Linnros, V. Grivickas, U. Lindefelt, and C. Hallin, Appl. Phys. Lett. 71, 3269 (1997).

- [3] K. Tanaka, K. Nagaya, and M. Kato, Jpn. J. Appl. Phys. 62 SC1017 (2023).

- [4] T. Miyazawa, T. Tawara, R. Takanashi and H. Tsuchida, Appl. Phys. Express 9 111301 (2016).

- [5] K. Murata, T. Tawara, A. Yang, R. Takanashi, T. Miyazawa, and H. Tsuchida, J. Appl. Phys. 126, 045711 (2019).

- [6] N. Achtziger and W. Witthuhn, Phys. Rev. B 57, 12181 (1998).

- [7] W. C. Mitchel, W. D. Mitchell, G. Landis, H. E. Smith, W. Lee, and M. E. Zvanut, J. Appl. Phys. 101, 013707 (2007).

- [8] K. Murata, T. Tawara, A. Yang, R. Takanashi, T. Miyazawa and H. Tsuchida, J. Appl. Phys. 129 (2021).

# ⑥ 大電流パルス動作時におけるキャリア再結合のモデル化とキャリアライフタイム制御(担当: (株) 日立製作所)

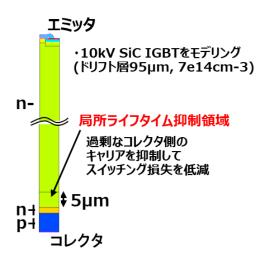

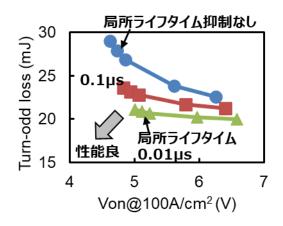

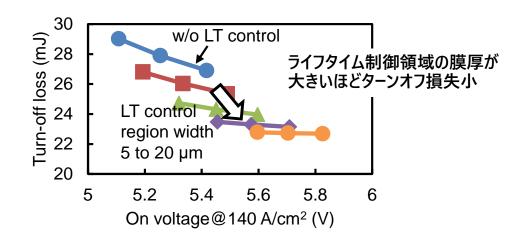

キャリアライフタイム制御においては、10 kV SiC IGBT (厚膜エピ)における伝導度変調動作、オン電圧 (Von)-スイッチング損失 (Esw)のトレードオフ改善が課題である (図6-1)。図6-2に示すシミュレーションモデルを用い、ドリフト層ライフタイムとVon-Eswの関係、そのトレードオフをデバイスシミュレーションにより評価した。ドリフト層全体のライフタイムを向上させることで十分に伝導度変調しVonが5V以下が実現可能であり、局所ライフタイム抑制によりVon-Eswのトレードオフが改善することを明らかにした(図6-3)。

図6-1 SiC IGBTにおける伝導度変調動作

図6-2 シミュレーションに用いたモデル

図6-3 オン電圧とスイッチング損失の関係

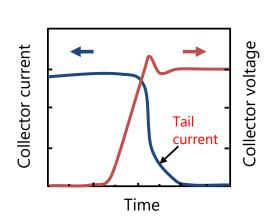

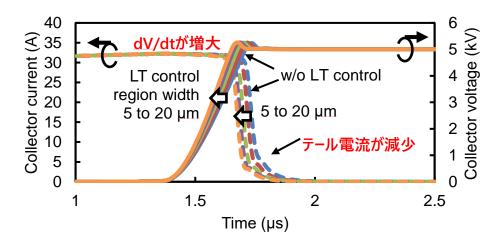

局所キャリアライフタイム制御によるデバイス特性改善を検討した。10 kV SiC IGBTの伝導度変調動作によりドリフト層抵抗が低減しオン電圧が減少するが、一方、図6-4に模式的に示すSiC IGBTのターンオフ波形のように、ターンオフ動作時に発生する残留電荷によるテール電流によりスイッチング損失が増大する。局所キャリアライフタイム制御においては、このオン電圧(Von)-スイッチング損失(Esw)のトレードオフ改善が課題である。図6-5に示すシミュレーションモデルを用い、局所キャリアライフタイム制御領域について、ライフタイムはプロセス上実現可能な値である $0.5 \mu$  sとし、膜厚を変化させた場合のオン電圧とターンオフ特性への影響をデバイスシミュレーションにより評価し、Von-Eswの関係、そのトレードオフを明らかにした。

図 6-4 SiC IGBT ターンオフ特性の模式図

図 6-5 SiC IGBT 局所キャリアライフ タイム制御のシミュレーションモデル

図6-6に局所キャリアライフタイム制御領域の膜厚(LT control region width)を $5~\mu$ mから  $20~\mu$ mまで変化させた場合のターンオフ特性を示す。図中の青線がキャリアライフタイム制御を 行わない場合の特性であるが、局所キャリアライフタイム制御によりテール電流が減少し、膜厚を増大することによりその効果が大きくなる。また電圧の変化速度(dV/dt)が局所キャリアライフタイム制御により増大しているが、これはオン時のドリフト層中のキャリア濃度が減少しているためであり、オン電圧も局所キャリアライフタイム制御により増大した。そこで、オン電圧とスイッチング損失の関係を図6-7に示す。オン電圧とスイッチング損失のトレードオフが改善していることが分かる。一方、膜厚が $15~\mu$ mと $20~\mu$ mではターンオフ損失はほとんど変わらず、局所キャリアライフタイム制御構造の膜厚には最適値が存在することを明らかにした。以上のように得られた知見をもとに、実デバイス試作に向けた局所キャリアライフタイム制御構造の仕様を設計し、エピタキシャル成長を実施した。

図 6-6 局所キャリアライフタイム制御の膜厚を変化させた場合の SiC IGBT ターンオフ特性

図 6-7 局所キャリアライフタイム制御の膜厚を変化させた場合の オン電圧とスイッチング損失の関係

局所キャリアライフタイム制御を適用したSiC PNDを試作し、スイッチング特性からライフタイム制御技術効果を検証した。図6-8に使用したSiCエピ基板の断面図を示す。図6-8 (a)の標準仕様では、ドリフト層のキャリアライフタイムは10  $\mu$ secであるが、(b)の局所ライフタイム制御仕様では、ドリフト層の再表面20  $\mu$ mのキャリアライフタイムを1  $\mu$ secと短く設定した。図6-9に標準仕様のSiC PNDのリカバリ特性を示す。得られたリカバリ損失は標準仕様で47  $\mu$ mJ/cm²であり、局所ライフタイム制御によりリカバリ損失は約13%減少した。SiC PNDにおいて局所ライフタイム制御がリカバリ損失低減に効果があることを実証した。局所キャリアライフタイム制御を適用したSiC IGBT試作に関しては図6-10に局所キャリアライフタイム制御を適用したSiC IGBTオン時のコレクタ電流 - 電圧特性を示す。図6-8に示したエピ構造上にデバイスを試作、具体的設計数値を表6-1に示す。図6-7に示したシミュレーション結果と同傾向のオン電圧特性を実現した。

図 6-8 局所キャリアライフタイム制御を 適用した SiC エピ基板

図 6-9 標準仕様の SiC PND のリカバリ特性

図 6-10 局所キャリアライフタイム制御を適用した SiC IGBT オン時のコレクタ電流 - 電圧特性

|     | n ドリフト 1   |                       |                   | n ドリフト 2   |                       |                   |

|-----|------------|-----------------------|-------------------|------------|-----------------------|-------------------|

| No. | 膜厚<br>(mm) | ドーピング<br>密度<br>(cm-3) | Life time<br>(μs) | 膜厚<br>(mm) | ドーピング<br>密度<br>(cm-3) | Life time<br>(µs) |

| 1   | 95         | 7E+14                 | 10                | -          | -                     | -                 |

| 2   | 10         | 7E+14                 | 1                 | 85         | 7E+14                 | 10                |

| 3   | 20         | 7E+14                 | 1                 | 75         | 7E+14                 | 10                |

表 6-1 局所キャリアライフタイム制御を適用した SiC IGBT 試作のエピ構造

#### ⑧大電流パルス動作時における積層欠陥のモデル化と電気特性への影響評価

#### (担当:(一財)電力中央研究所)

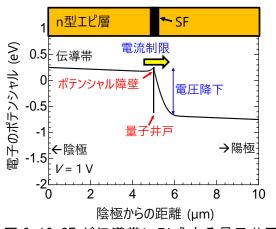

SiC-IGBT の大電流パルス出力時における積層欠陥(SF)の拡大の有無や、積層欠陥がデバイスの電気特性に与える影響の評価に向けて、デバイス動作温度領域(室温から  $250^{\circ}$ C)での積層欠陥(SF)の拡大に関わる物理的パラメータ(積層欠陥エネルギー)を評価するための新たな測定手法を開発するとともに、各種 SF がデバイスの電気的特性に与える影響の解明を進め、以下の成果を得た。

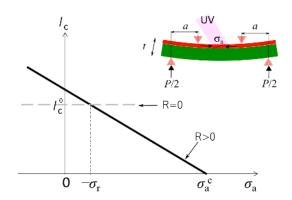

#### 8.1 積層欠陥形成エネルギーの測定

SiC-IGBT や PiN ダイオードなどのバイポーラデバイスにおいて、PN 接合への順方向通電により(31)型積層欠陥(シングルショックレー型積層欠陥(1SSF))が拡大し、デバイスの通電特性が劣化することが課題である。順方向バイアスにより少数キャリアが注入されると、少数キャリア密度の増加に伴って単位面積当たりの実効的な 1SSF の形成エネルギーが Dg だけ低下する。少数キャリア密度(順方向電流)がある値を超えると、実効的な 1SSF の形成エネルギーが熱平衡状態における形成エネルギー $g^{eq}$  を超えて負に転じ、1SSF が拡大すると理解されている。したがって、 $g^{eq}$  は積層欠陥の拡大が開始する順方向電流の閾値を支配する重要な物理パラメータとなる。

熱平衡状態の 1SSF 形成エネルギー $g^{eq}$ の評価値として、透過型電子顕微鏡による観察結果から得られた値  $g^{eq}=14$  ± 2.5 mJ/m² が報告されている[1]。しかし、測定対象とした転位は高温 (1300°C)の塑性変形により導入されており、室温付近での  $g^{eq}$  を反映しているかは不明である。また、透過型電子顕微鏡観察では薄膜試料が用いられていることも懸念点である。そこで、バルク試料を用いた非破壊実験により室温付近の低温で  $g^{eq}$  値を測定評価する手法を開発した[2]。

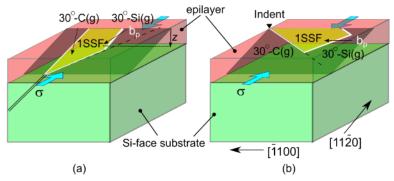

1SSFを挟んで拡張した部分転位(PD)対の内、 $30^\circ$  -Si(g)と呼ばれる過剰半平面がSi原子で終端するPDが1SSFの拡大を担い、C原子で終端する $30^\circ$  -C(g) PDは動かないことが知られている。このために、1SSFが拡大する方向に機械的な外応力を加えて $30^\circ$  -Si(g) PDを動かすことで1SSFの拡大を促すことができる。一方で $g^{eq}$  は1SSFを縮小させる力として働き、少数キャリア注入量/における正味の1SSF拡大駆動力は次式で与えられる。

$$\Delta \gamma(I) + R\sigma b_n - \gamma^{eq.} \tag{1}$$

ここでのは結晶中に働く垂直応力、Rはのに比例して 1SSF を拡大する方向へ 30°-Si(g) PD を移動させる分解せん断応力を与える比例係数(シュミット因子)、 $b_0$  は PD のバーガースベクトルの大きさである。1SSF 拡大駆動力が 0 となり 1SSF が拡大も縮小もしない少数キャリア注入量を与える臨界光強度  $I_0$ の $\sigma$ 依存性を測定し、 $I_0$ =0 となる外挿値 $\sigma$ を求めることで、 $g^{eq}$  は  $R\sigma^c b_p$ の値で評価できる(図 8.1)。

実際にはエピ膜中に残留応力 $\sigma_r$ が存在する可能性があり、PD に働く応力 $\sigma$ は外応力 $\sigma_a$ に加えて残留応力 $\sigma_r$ を考慮する必要がある( $\sigma = \sigma_a + \sigma_r$ )。

図 8.1 1SSF 形成エネルギー評価の 原理[2]

図8.2 1SSF 形成エネルギー評価実験 装置の概要[2]

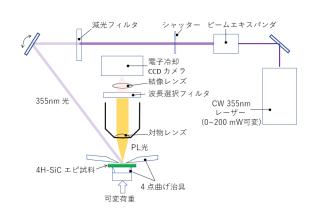

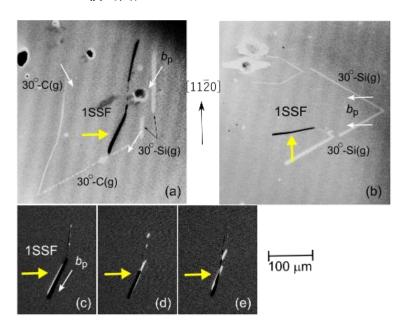

本実験では紫外 (UV) 光照射を用いて Dgを生じさせ、フォトルミネッセンス (PL) イメージングにより1SSFやPDを観察した (図8.2) [2]。UV光の光源には波長355 nmのCWレーザー装置を用いた。図8.3 (a) は基板から伝搬した板状試料に対し、4点曲げステージを用いて曲げ荷重を加えた。図8.3 (a) は基板から伝搬した底面転位 (BPD) よりUV光の強照射で拡大させたR>0のタイプの1SSF、(b) は表面に刻印した微小圧痕からUV光の強照射で拡大させたR=0のタイプの1SSFの模式図を示す [2]。P 型試料で観察された PL 像を図 8.4 に示す [2]。P (a) と (b) は P>0 タイプ, P=0 タイプの 1SSF で

図 8.3 実験に用いたエピ試料の結晶方位((a) R>0 のタイプ、(b) R=0 のタイプの 1SSF の模式図)

図 8.4 SF と PD の PL イメージング画像 [2]

ある。黒のコントラストは、 $I_0$ より低い強度で一定時間 UV 光を照射した直後の PL 像を白黒反転させて照射直前の PL 像に重ねたものである。図 8.4(c),(d),(e)は UV 光強度が  $I_0$ より高い場合、低い場合、近い場合の PL 像(重ね合わせ像)をそれぞれ示している。

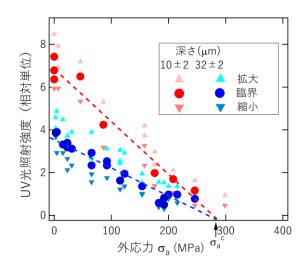

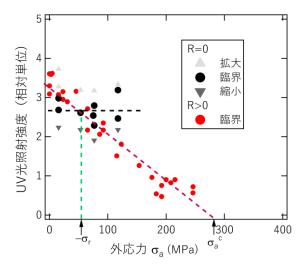

以上の評価法を用いて、p 型結晶中の R0 タイプの 1SSF が拡大、縮小、臨界状態となる照射強度 ( $I_c$ に相当)を評価した結果を外応力  $s_a$ の関数として示す(図 8.5)[2]。測定される臨界強度  $I_c$ は、1SSF の表面からの深さに依存するが、得られた  $I_c$ - $\sigma$ 関係を直線外挿できると仮定して求めた  $\sigma_a$  の値は、1SSF の深さに依存しない共通の値 ( $\sigma_a$  = 280±50 MPa)となった。残留応力  $\sigma_r$  を評価するために、同じ試料でほぼ同じ深さに導入された R-0 タイプの 1SSF についてその  $I_c$ - $\sigma$ 関係を測定した結果を図 8.6 に示す [2]。 R-0 タイプの 1SSF について測定した  $I_c$ - $\sigma$ 関係との交点から、この試料の残留応力は  $s_r$  = 50 ± 30 MPa と評価された。図 8.5, 8.6 の結果から  $g^{eq}$  = R- $g^{eq}$  +  $g^{eq}$  =  $g^{eq}$  +  $g^{eq}$  =  $g^{eq$

図 8.5 1SSF の拡大・縮小を起こす UV 光 強度の外応力依存性 [2]

図 8.6 残留応力評価に用いた R=0 タイプと R>0 タイプの 1SSF の拡大・縮小を画する UV 光強度の外応力依存性 [2]

#### 8.2 各種の積層欠陥が電気的特性に与える影響の解明(ユニポーラデバイス)

#### 8.2.1 デバイス作製プロセス

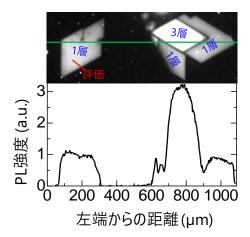

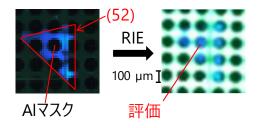

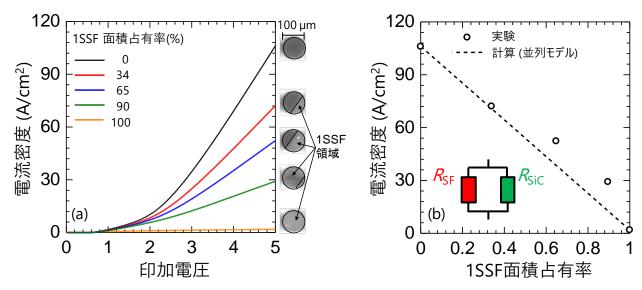

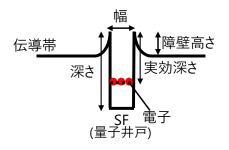

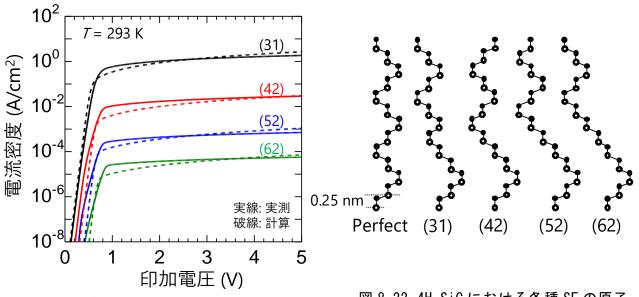

n型エピ膜(膜厚34  $\mu$ m、ドーピング密度3×10<sup>14</sup> cm<sup>-3</sup>)を用いて、複数種のSFをデバイス動作領域に内包するSBDを作製した(図8.7)[3]。PLイメージング観察および低温におけるスペクトル測定により、エピ膜中の積層欠陥の位置および種類を特定した[4-6]。成長時に導入されたSF種は、Zhdanovの表記法で(42)、(52)、(62)型であった(図8.8)。また、SiCエピ膜上に微小圧痕を形成し、波長325 nmのレーザー光を照射することで(31)型である1SSF[7-9]を形成した。図8.9に発生させた1SSF近傍領域のPLイメージング像を示す[3]。PL像の下のグラフはPL像中の緑線に沿って得られたPL発光強度分布である。PL像の右側に観測される複数枚の1SSFのPL強度は、左側の1SSFのPL強度の3倍となっており、左側の1SSFは1層であると考えられる。

図8.10に示すように、反応性イオンエッチング (RIE) を用いてデバイス動作領域にSFを面積占有率100%で内包するSBDを作製した[3]。AI金属(直径100  $\mu$ m, 厚さ400 nm)をフォトリソグラフィによりSFを含む領域上に形成し、RIE時のマスクとして用いた。素子分離後、Ni電極を両面に堆積し、電極アニール(1000°C 2 min)を施した。

図8.7 動作領域に面積占有率 100%でSFを内包するSiC SBDの 模式図[3]

図 8.8 ウェハ面内に観測された SFの PL イメージング像

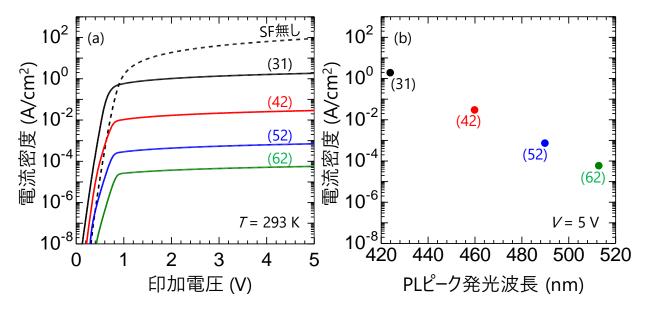

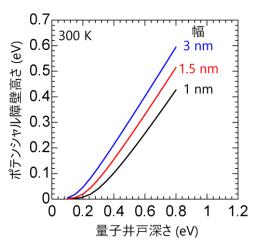

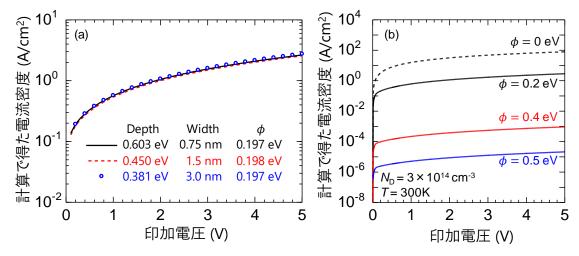

#### 8.2.2 各種SFを有するSBDの電気特性

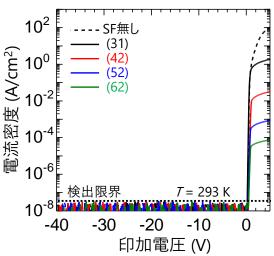

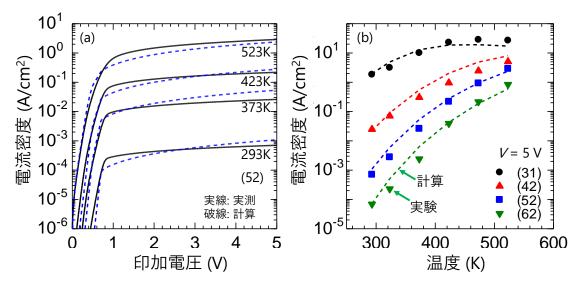

図8.11(a)に293 Kにおける各種SFをデバイス動作領域に面積占有率100%で内包するSBDのI-V特性の測定結果を示す。SBD通電時の電流密度はSFを内包することで大きく制限され、印加電圧1 V以上の電流密度から見積もられるSBDのコンダクタンスは内包するSF種に依存して大きく変動することが明らかになった。印加電圧5 Vにおける電流密度とSFのPLピーク発光波長の関係をプロットした結果を図8.11(b)に示す[3]。PLピーク発光波長が長くなるにつれて、電流密度の制限度

合いが大きくなっている。

図8.12に、SFが伝導帯に形成する量子井戸[10-12]をモ デル化(8.3.1節参照)し、1SSFを内包するn型4H-SiCエピ 膜の1 V印加時における電気伝導をデバイスシミュレーシ ョンにより求めた結果を示す[13]。この結果から、1SSFが 形成する量子井戸が電子をトラップすることでポテンシ ャル障壁を形成し、その障壁が電気伝導を制限することが 明らかになった。図8.11(b)の結果は、PLピーク発光波長が 長いSFほど伝導帯に形成される量子井戸が深いことを示 唆しており、深い量子井戸が高密度に電子をトラップする ことで、より高いポテンシャル障壁を形成していると考え られる。なお、印加電圧1 V以下の低電圧領域における順方 向I-V特性が各SBDにより多少異なっていたが、その理由は ショットキーコンタクトの仕事関数のばらつきである。仕 事関数のばらつきはSF種には依存しないことを確認して おり、再現性も無いため、RIEによる表面ダメージ等に起因 していると考えられる。また、SFを内包するSBDの293 Kに おける印加電圧-40 Vまでの逆方向I-V特性を測定した結 果、逆方向リーク電流は検結果、逆方向リーク電流は検出 限界(10 pA)以下であった(図8.13)[3]。

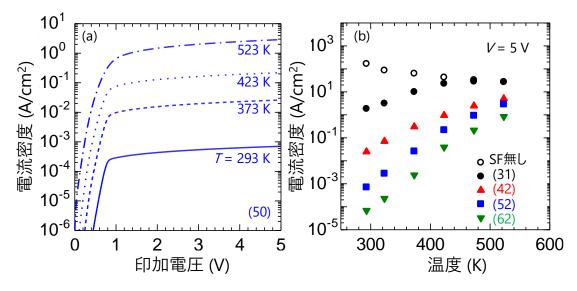

図8.14(a)は、(52)型SFを内包するSBDの様々な温度における順方向I-V特性を評価した結果を示す[3]。温度の上昇に伴い、SFによる電流制限効果が弱まり、SBDのコンダクタンスが増大した。温度上昇につれて、熱放出により量子井戸内にトラップされている電子密度が低下し、SFが伝導帯に形成するポテンシャル障壁の高さが低くなる。8.3.1節

図 8.9 形成した 1SSF の PL イメージング像(上図)と像中の緑線上における PL 発光強度分布(下図)[3]

図 8.10 RIE 実施前(左図)および後(右図)の PL イメージング像 (左図中の赤線: SF 領域の境界 線)[3]

図 8.11 (a)作製した SBD の 293 K における順方向 I-V 特性、(b)印加電圧が 5 V における電流密度の PL ピーク発光波長依存性[3]

図 8.12 SF が伝導帯に形成する量子井戸およびそれによる電流制限機構の模式図[13]

図 8.13 作製した SBD の 293 K における逆方向 I-V 特性[3]

に述べるように、高温では高エネルギー電子密度が増大し、ポテンシャル障壁を越える電子密度が高くなる。これら2つの効果により、高温ではSFの電流制限効果が弱まることを説明できる。

図8.14(b)は、各種SFを含むSBDの順方向I-V特性において印加電圧が5 Vにおける電流密度の温度依存性を評価した結果を示す[3]。SFを内包するSBDの電流密度は温度上昇とともに増大したのに対し、SFを内包しないSBDは温度上昇に伴い電流密度が低下した。SFを内包しないSBDの電流密度の温度依存性は、電子移動度の温度依存性に起因すると考えられる[14,15]。また、473 K以上において、1SSFを内包するSBDの電流密度は、SFを有さないSBDの値と一致している。このことは、1SSFが形成するポテンシャル障壁の電気伝導への影響が473 K以上では実質的に無視できることを示す。一方、(42)、(52)、(62)型SFについては、伝導帯に形成するポテンシャル障壁が高く、473 K以上の温度でも影響を無視できない。

図 8.14 (a)(52)型 SF を内包する SBD の順方向 I-V 特性の温度依存性、(b)各 SBD の順方向 I-V 特性において印加電圧が 5 V における電流密度の温度依存性[3]

図8.15 (a) 様々な面積占有率で1SSFを部分的に内包するSBDの順方向I-V特性(挿入図:部分的に1SSF(明領域)を内包するSBDの $PLイメージング像)、(b) 印加電圧が5 Vにおける電流密度の1SSF面積占有率依存性(挿入図: SFを部分的に有するSBDの等価回路モデル(<math>R_{SF}$ : 1SSF占有領域の直列抵抗、 $R_{SiC}$ : 非占有領域の直列抵抗))[3]

次に、1SSFを部分的に内包するSBDの順方向I-V特性を取得し、デバイス動作面積に対する1SSFの面積占有率との関係を評価した(図8.15(a))[3]。PLイメージング像(図8.15(a)挿入図)において明領域が1SSFに占有されている領域、暗領域がSFを有さない領域を示しており、その割合からSFの占有率を求めた。1SSFの面積占有率の上昇に伴い、順方向電流のコンダクタンスが単調に低下した。印加電圧5 Vにおける電流密度の1SSF面積占有率依存性を図8.15(b)に示す[3]。1SSF占有領域と非占有領域が動作面積内で並列接続しているモデル(図8.15(b)挿入図)に基づき、計算により求めた電流密度と1SSFの面積占有率の相関関係を破線で示した。実験結果と計算は概ね一致しており、並列接続モデルが妥当であることを示す。なお、計算値に比べ実験値が高い値を示す理由として、SF非占有領域における電流拡がり現象が考えられる。

#### 8.3 各種の積層欠陥をモデル化

8.3.1 シミュレーションしたデバイス構造および計算条件 SFがSiCデバイスの通電特性に与える影響の解明を目的と して、デバイスシミュレータ(TCAD)を用いてSFを内包する n型SiC膜の電流-電圧特性を解析した。シミュレーションに 用いたデバイス構造(ドーピング密度: 3×10<sup>14</sup> cm<sup>-3</sup>、膜厚: 34 μm) を図8.16に示す[16]。デバイス動作面積の全面にわ たり、上部電極から5 µm下の位置にSFを挿入した。なお、 シミュレーションにより得られる電気特性は、エピ膜中の SFの位置に強く依存しないことを確認している。図8.17に SFにより形成される伝導帯における量子井戸の模式図を示 す[16]。量子井戸が電子を捕獲することで井戸内に電子が 蓄積し、ポテンシャル障壁が形成される。電子蓄積により エネルギーが高くなっている伝導帯と井戸内の基底準位と のエネルギー差を実効井戸深さと定義した。なお、井戸内 の基底準位はシュレディンガーポアソン方程式を解くこと で得た。図8.18にシミュレーションにより得られた印加電 圧0 V、温度300 Kにおけるポテンシャル障壁高さの井戸幅 および深さ依存性を示す。本モデルでは、量子井戸は深さ と幅のパラメータで定義しており、これら2つのパラメータ

図 8.16 シミュレーションした素子のデバイス構造[16]

図 8.17 SF により形成される伝導帯における量子井戸の模式 図[16]

によりポテンシャル障壁高さが変化する。

電圧印加時の定常状態における通電特性は、電流の連続およびポアソン方程式を解くことで得た。その際、Bohm quantum potential (BQP) モデル[17]を取り入れることで、量子井戸における量子論的効果を考慮した。BQPモデルでは、位置依存する量子補正ポテンシャルを導入することでトンネル効果やキャリア束縛などの量子論的効果を考慮できる。

#### 8.3.2 SFを内包するn型エピ膜の通電特性の制限因子

図8. 12に示したシミュレーション結果から、SFによる電流制限は伝導帯に形成されるポテンシャル障壁により生じると考えられるため、通電特性とポテンシャル障壁高さの関係を調べた。図8. 19 (a) に異なる井戸構造のSFを有するn型SiC膜の通電特性を示す[16]。深さと幅が異なるが、形成されるポテンシャル障壁高さは約0. 2 eVと同等である。同図より、ポテンシャル障壁高さがが高い同等である場合、通電特性も同等になることが分かる。図8. 19 (b) に様々なポテンシャル障壁高さにおけるn型SiC膜の通電特性を示す[16]。なお、障壁高さは、井戸の深さと幅を変化させることで、0-0.5 eVの範囲で調整した。電流コンダクタンスは障壁高さが高くなるにつれて指数関数的に低下することが示された。

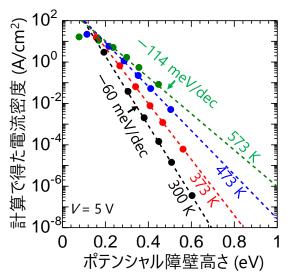

図8.20にシミュレーションにより得たn型SiC膜の電流密度(印加電圧5 V)のポテンシャル障壁高さ依存性を示す[16]。破線で示されるように、300、373、473、

図 8.18 SF により形成される伝導帯 におけるポテンシャル障壁高さの井 戸深さおよび幅依存性[16]

573 Kにおいて、電流密度は障壁高さが高くなるにつれてそれぞれ-60、-74、-94、-114 meV/dec の変化率で低下した。

伝導帯に存在する電子は、ボルツマン分布に従ってエネルギーに対して分布するため、障壁高さ $\phi$ を超える電子密度は、 $n=n_0\exp(-e\phi/kT)$ で表される。ここで、 $n_0,k,e$  および T は、それぞれ SFを含まないエピ膜中の電子密度、ボルツマン定数、素電荷、絶対温度である。ポテンシャル障壁を越える電子密度は熱電圧 (-kT/e) で決まり、その温度に対する変化率は、シミュレーションにより得られた電流密度のポテンシャル障壁高さに対する変化率と一致した。したがって、SFを有する n型 SiC 膜の電流密度 J はポテンシャル障壁を越える電子密度で制限され、J  $\propto n_0\exp(-e\phi/kT)$  で表されると考えられる。

図 8. 19 (a) シミュレーションにより得た SF を有する SiC 膜の 300 K における通電特性、(b) シミュレーションにより得た SF を有する SiC エピ膜の 300 K における通電特性[16]

図 8. 20 n 型 SiC 膜の電流密度(印加電圧: 5 V)のポテンシャル障壁高さ依存性のシミュレーション結果[16]

## 8.3.3 各種のSFの量子井戸深さおよび幅

8.2.2節の議論に基づき、SFを有するn型SiC膜の電流制限度合いは、ポテンシャル障壁高さを反映していると解釈でき、8.1.2節において実測した4種のSFを内包するSBDの通電特性(図8.11)をもとに、各種SFが伝導帯に形成するポテンシャル障壁の障壁高さを見積もった。障壁高さは量子井戸深さおよび幅に依存することから、障壁高さから井戸構造を決定できる。

図8.21にSFを内包するSBDの電気特性の実測結果およびシミュレーション結果を示す。本研究では、先行研究[18,19]に基づいて、量子井戸深さを0.87 eVと仮定し、井戸幅を決定した。得られた井戸幅を表8.1に示す。井戸幅は各種SFの30構造の物理的厚さに対応している。(31)、(42)、(52)、(62)型の30構造の物理的厚さはそれぞれ0.75, 1.0, 1.25, 1.5 nmである(図8.22)[16]。

図 8.21 各種 SF を内包する SBD の 293 K における電気特性の実測値とシミュレーションの比較[16]

図 8.22 4H-SiC における各種 SF の原子 構造(黒丸: C 原子、白丸: Si 原子) [16]

(52)型SFを内包するSBDの様々な温度における電気特性の実測結果と、表8.1に示したパラメータ(量子井戸の深さおよび幅)を用いて得られたシミュレーション結果を図8.23(a)に示す[16]。表8.1のパラメータは293 Kにおける電気特性に基づいて導出した値であるが、各温度におけるシミュレーション結果と実測結果は良く一致した。図8.23(b)に各種SFを内包するSBDの印加電圧5 Vにおける電流密度の実験結果およびシミュレーション結果を示す[16]。いずれの型のSFを有するSBDの電気特性に対しても、広い温度範囲の実験結果を再現しており、提案した量子井戸モデルが有効であることを示す。

表8.1において、提案した量子井戸モデルにおける量子井戸内の基底準位と価電子帯端とのエネルギー差 $E_{GL}$ - $E_{V}$ と、SFからのPLピークエネルギーの値を比較すると、(31)型SFに対しては、 $E_{GL}$ - $E_{V}$ と 2.92 eVとPLピークエネルギーに近くなっている。一方で、(42), (52), (62)型SFに対しては、PLピークエネルギーが $E_{GL}$ - $E_{V}$ に比べて小さく、量子井戸幅が広がるにつれて差が顕著となっている。要因の一つとして井戸内の分極に起因する内部電界(Stark効果)の関与が考えられる[23, 24]。

図 8. 23 (a) (52) 型の SF を内包する SBD の電気特性の温度依存性の実測とシミュレーション結果 (実線:実験結果、破線:シミュレーション)、(b) 各種 SF を内包する SBD の印加電圧が 5 V における電流密度の温度依存性の実験結果 (シンボル) とシミュレーション結果 (破線) [16]

表 8.1 各種 SF に対応するデバイスシミュレーション用の量子井戸モデル[16] (PL ピークエネルギーは先行研究([20-22])で求められた値)

| SF種  | 障壁高さ(eV)<br>293 K,<br>N <sub>D</sub> =3×10 <sup>14</sup> cm <sup>-3</sup> | 幅 (nm) | 深さ (eV)<br>(実効深さ) | 基底準位と価電子帯端<br>のエネルギー差(eV)<br>( <i>E</i> <sub>GL</sub> - <i>E</i> <sub>V</sub> ) | PLピーク<br>エネルギー(eV) |

|------|---------------------------------------------------------------------------|--------|-------------------|---------------------------------------------------------------------------------|--------------------|

| (31) | 0.2                                                                       | 0.43   | 0.87<br>(0.34)    | 2.92                                                                            | 2.92 – 2.99        |

| (42) | 0.31                                                                      | 0.58   | 0.87<br>(0.46)    | 2.80                                                                            | 2.70 – 2.76        |

| (52) | 0.38                                                                      | 0.71   | 0.87<br>(0.54)    | 2.72                                                                            | 2.59 – 2.53        |

| (62) | 0.45                                                                      | 0.87   | 0.87<br>(0.61)    | 2.65                                                                            | 2.41 – 2.46        |

#### 8.3.4 バイポーラ素子における1SSFによる電気特性悪化メカニズム

1SSFによりPiNダイオードの電流が制限されるメカニズムに関して、デバイスシミュレーションを用いて調べた。図8.24にシミュレーションに用いたPiNダイオードのデバイス構造を示す [25]。1SSFは量子井戸として扱い、量子井戸パラメータ(井戸幅、深さ)は表8.1に示す値を用いた。キャリア再結合モデルには、Shockley-Read-Hall (SRH)モデル、直接再結合モデル、およびAuger再結合モデルの3つの再結合モデルを採用した。ここでは、SRHモデルのパラメータ Aを1  $\mu$ s、直接再結合係数 Bを1.5×10 $^{-12}$  cm $^3$ /s、オージェ再結合係数  $C_n$ を5.0×10 $^{-31}$ cm $^6$ /sとして計算を行った [26]。

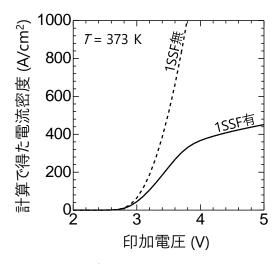

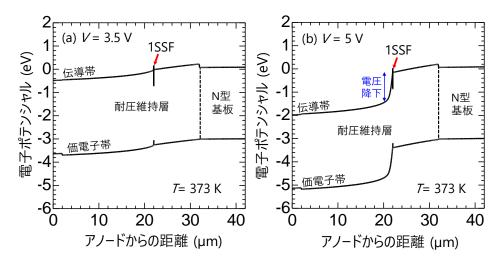

373 Kにおける順方向 *I-V*特性のシミュレーション結果を図8.25に示す[25]。実線は1SSFを内包する素子、破線は1SSFを含まない素子の特性である。1SSFを有するPiNダイオードの順方向電流は1SSFにより制限を受けることが示されており、特に電圧~4 V以上において顕著な電流制限効果が現れている。

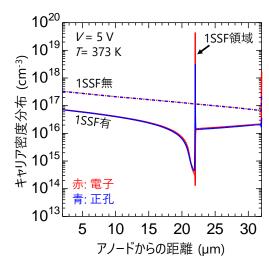

印加電圧3.5 Vおよび5 Vにおけるポテンシャル プロファイルを図8.26(a)、(b)に示す[25]。印加 電圧3.5 Vにおいては1SSFが形成する空乏層にお ける電圧降下は顕著には生じず、5 Vでは大きな電 圧降下が生じた。3.5 V印加時に1SSFによる電圧降 下が生じない要因は、伝導帯に加わる電界による 電子電流に加えて、価電子帯を流れる正孔電流お よび再結合電流が存在することによる。印加電圧 5 Vでは、図8.27に示すように耐圧維持層内に注入 される過剰キャリア密度が高くなり、量子井戸に よる電子トラップによって量子井戸近傍のキャリ ア密度が高くなる。キャリア密度が高まることで、 直接再結合およびAuger再結合の寄与が高まり、キ ャリアライフタイムが短くなるため(図5.7)、耐 圧維持層内のキャリア密度は小さくなる。これに よって正孔電流・再結合電流の寄与が低下し、電 子・正孔によるキャリア伝導から単一キャリア(電

図8.24 PiNダイオードのシミュレーションに用いたデバイス構造[25]

図8.25 PiNダイオードの電流-電圧特性 のシミュレーション結果[25]

子)のみのキャリア伝導に近いものへと変化する。電界による電子のドリフト電流は、ポテンシャル障壁の影響を受けるため、1SSFによる電圧降下が生じる。

以上をまとめると、PiNダイオードにおいて、1SSFにより電気特性が悪化するメカニズムは以下の4つのプロセスによると説明できる。

- 1) 積層欠陥が形成する量子井戸に電子が高密度に蓄積し、その近傍にクーロン引力により正孔 密度が増大

- 2) 積層欠陥近傍で再結合速度が高まり、局所的にキャリアライフタイムが低下

- 3) ドリフト層中の正孔密度が低下し、正孔電流の寄与が低下

- 4) ポテンシャル障壁による電子伝導制限効果が顕在化

図8.26 印加電圧が(a) 3.5 Vおよび(b) 5 Vにおける1SSFを内包するPiNダイオードの耐圧維持層内のポテンシャルプロファイル[25]

図8.27 シミュレーションにより得た耐圧維 持層内のキャリア密度分布[25]

#### 参考文献

- [1] M. H. Hong, A. V. Samant, and P. Pirouz, Phil. Mag. A 80, 919 (2000).

- [2] K. Maeda, K. Murata, I. Kamata, and H. Tsuchida, Appl. Phys. Express 14, 044001 (2021).

- [3] S. Asada, K. Murata, H. Tsuchida, Appl. Phys. Express 15, 045502 (2022).

- [4] I. Kamata, X. Zhang, and H. Tsuchida, Appl. Phys. Lett. 97, 172107 (2010).

- [5] H. Uehigashi, K. Fukada, M. Ito, I. Kamata, H. Fujibayashi, M. Naitou, K. Hara, H. Osawa, T. Kozawa, and H. Tsuchida, Mater. Sci. Forum 858, 173 (2016).

- [6] S. G. Sridhara, F. H. C. Carlsson, J. P. Bergman, and E. Janzén, Appl. Phys. Lett. 79, 3944 (2001).

- [7] H. Lendenmann, B. Peder, D. Fanny, and C. Hallin, Mater. Sci. Forum 433-436, 901 (2003).

- [8] J. D. Caldwell, R. E. Stahlbush, E. A. Imhoff, K. D. Hobart, M. J. Tadjer, Q. Zhang, and A. Agarwal, J. Appl. Phys. 106, 044504 (2009).

- [9] K. Murata, T. Tawara, A. Yang, R. Takanashi, T. Miyazawa, and H. Tsuchida, J. Appl. Phys. 126, 045711 (2019).

- [10] H. Iwata, U. Lindefelt, S. Öberg, and P. R. Briddon, J. Appl. Phys. 93, 1577 (2003).

- [11] M. Camarda, A. La Magna, P. Delugas, and F. La Via, Appl. Phys. Express 4, 025802 (2011).

- [12] K. B. Park, J. P. Pelz, J. Grim, and M. Skowronski, Appl. Phys. Lett. 87, 232103 (2005).

- [13] S. Asada, T. Miyazawa, and H. Tsuchida, Jpn. J. Appl. Phys. 59, 054003 (2020).

- [14] J. Pernot, S. Contreras, J. Camassel, J. L. Robert, W. Zawadzki, E. Neyret, and L. Di Cioccio, Appl. Phys. Lett. 77, 4359 (2000).

- [15] H. Iwata and K. M. Itoh, J. Appl. Phys. 89, 6228 (2001).

- [16] S. Asada, K. Murata, and H. Tsuchida, IEEE Trans. Electron Devices 68, 3468 (2023).

- [17] G. Iannaccone, G. Curatola, and G. Fiori, Int. Con. on Simulation of Semiconductor Processes and Devices. Berlin, Germany: Springer Verlag, 275 (2004).

- [18] H. Iwata, U. Lindefelt, S. Öberg, and P. R. Briddon, J. Appl. Phys., 93, 1577 (2003).

- [19] C. Taniguchi, A. Ichimura, N. Ohtani, M. Katsuno, T. Fujimoto, S. Sato, H. Tsuge, and T. Yano, J. Appl. Phys., 119, 145704 (2016).

- [20] H. Uehigashi K. Fukada, M. Ito, I. Kamata, H. Fujibayashi, M. Naitou, K. Hara, H. Osawa, T. Kozawa, and H. Tsuchida, Mater. Sci. Forum, 858, 173 (2016).

- [21] I. Kamata, X. Zhang, and H. Tsuchida, Appl. Phys. Lett., 97, 172107 (2010).

- [22] S. G. Sridhara, F. H. C. Carlsson, J. P. Bergman, and E. Janzén, Appl. Phys. Lett., 79, 3944 (2001).

- [23] J. Camassel and S. Juillaguet, J. Phys. D, Appl. Phys., 40, 6264 (2007).

- [24] H. Suo, T. Yamashita, K. Eto, A. Miyasaka, H. Osawa, T. Kato, and H. Okumura, Jpn. J. Appl. Phys., 61, 105502 (2022).

- [25] S. Asada, T. Miyazawa, and H. Tsuchida, IEEE Trans. Electron Devices 68, 3468 (2021).

- [26] A. Galeckas, J. Linnros, V. Grivickas, U. Lindefelt, and C. Hallin, Appl. Phys. Lett. 71, 3269 (1997).

## <u>⑩ 超高耐圧SiC IGBTを用いた大電力パルス電源高速・高信頼駆動手法の確立(担当:(株)</u> 日立製作所)

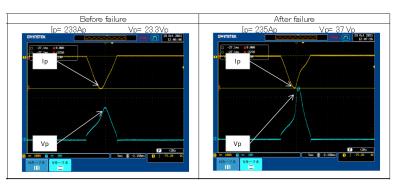

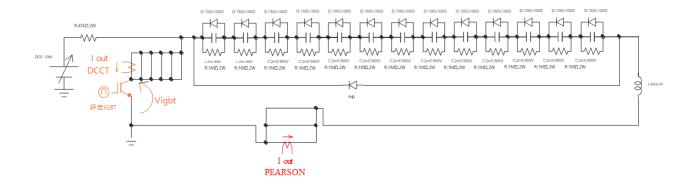

SiC IGBTミニモデルでのパルスピーク電流1 kAの実現に向けて、SiC IGBT 1チップに通流できるパルスピーク電流の限界値を評価した。図10-1に示すように1チップを簡易的に実装し、サンプルをベースプレートごと150度に設定したホットプレート上に置いた。ゲート-エミッタ間に20 Vを印加した状態で、コレクタ-エミッタ間にパルス幅10 msの正弦半波の電流を単発で印加し、耐圧が劣化するまで少しずつピーク電流値を上げながら試験したところ、図10-2に示すように230 A程度通流できることを確認した。

図10-1 SiC IGBTパルステストサンプル

図10-2パルス波形 (左)耐圧劣化直前、(右)耐圧劣化時

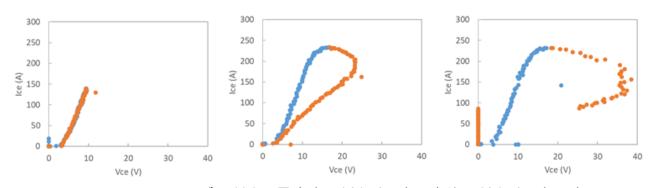

パルス波形を横軸電圧、縦軸電流にプロットし直した結果が図10-3のローカスカーブである。 青色はパルスの前半部分(0 - 5 ms)、燈色はパルスの後半部分(5 - 10 ms)を表している。小電流時はパルスの前半部分と後半部分が揃っており、対称的なパルスであることがわかる。一方、電流が大きくなるとパルスの前半部分と後半部分の電流-電圧特性が乖離しており、非対称なパルスになっている。また、230 A程度になるところで電流が飽和しており、それ以上の電流を流そうとして入力パワーを上げても電圧だけが上がっていく傾向を示している。チップを並列で利用する際は、特性の違いによってそれぞれのチップに流れる電流が異なってくる。そのため、飽和に近いところで動作させないほうがよいので、目標の1 kAを達成するには6チップ並列で利用するのがよいという指針を得た。

図10-3 ローカスカーブ (左)小電流時、(中)耐圧劣化直前、(右)耐圧劣化時

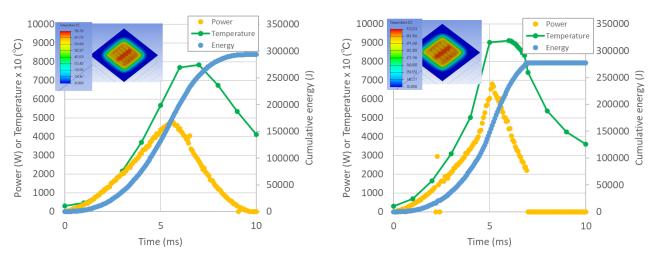

続いて、耐圧劣化時の状況を詳細検討した。図10-4はパルス波形の生データからパワー(電流×電圧)、エネルギー(パワーの時間積分)の時間変化を計算し、パワーの時間変化からチップ表面温度を有限要素シミュレーションによって計算した結果である。耐圧劣化直前のパルス印加時のエネルギーと、耐圧劣化時のエネルギーを比較すると、耐圧劣化時はパルス印加途中でチップが破壊していることから、耐圧劣化直前のほうでより高いエネルギーが発生している。しかしながら、チップ表面温度は耐圧劣化時のほうが高くなっており、温度起因で劣化したと考えられ

る。耐圧劣化直前には目視でチップに変化は見られなかったが、耐圧劣化時には音とともにチップから煙が発生し、チップの表面保護膜も黒く焦げている様子が見られた。煙(脱ガス)による圧力や、急激な温度変化に伴う応力によってチップの接合がダメージを受けてコレクタ-エミッタ間ショートに至ったと推測される。

図10-4 パルステスト時のパワー、エネルギー、温度の時間変化 (左) 耐圧劣化直前、(右)耐圧劣化時

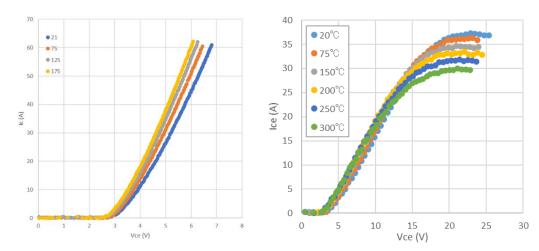

最後に、パルステスト時に観察された飽和電流について検討した。図10-5(左)はSiC IGBTの出力特性である。測定系のパワーが足りずに飽和特性が見えるところまで電流を印加できなかったため、アクティブ面積が1/10の小面積TEGの出力特性を測定したところ(図10-5(右))、飽和電流が温度とともに低下していくことがわかった。IGBTはMOS構造を有しており、MOS構造のチャネル部分の抵抗が温度とともに増加するために飽和電流が低下すると推測される。IGBTをインバータ用途で用いる際、上下アームが短絡した場合に備えて短絡耐量を確保するために飽和電流を下げる工夫が一般的に適用される。しかしながら、IGBTで大電流パルスを制御したいという用途においては、流せる電流上限が飽和電流で決まってしまうため飽和電流を上げることが有効である。具体的には、ユニットセルサイズを小さくしてセルをできるだけ多く敷きつめることが有効である。この考え方をデバイス構造の設計指針へとフィードバックした。

図10-5 SiC IGBTの出力特性の温度依存性 (左)本体チップ、(右)小面積TEG

本研究で目標とするSiC IGBTミニモデルでのパルスピーク電流1 kAの実現に向けて、SiC IGBT 1チップに通流できるパルスピーク電流量を増加させる手法を検討した。

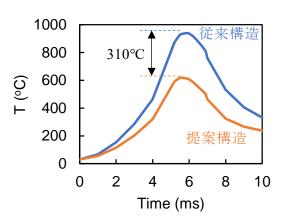

パルスピーク電流量はチップの飽和電流で決まり、その飽和電流は温度上昇と共に減少することを示した。また、現状のSiC IGBT 1チップへ通流可能な最大ピーク電流値は230 Aであることを実験から明らかにし、チップの特性バラつきを考慮すると目標の1 kAを達成するには6チップ並列で利用するのがよいという指針を得た。さらに、ピーク電流通流時のチップ表面温度は900℃近くまで上昇することを熱シミュレーションから明らかにした。以上を踏まえ、ピーク電流通流時のチップ表面温度を下げることで、SiC IGBT 1チップに通流できるパルスピーク電流量を増加させ、SiC IGBTミニモデルでのパルスピーク電流1 kAに必要なチップ数を減少できると考えた。

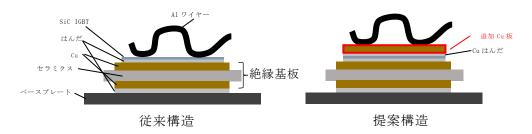

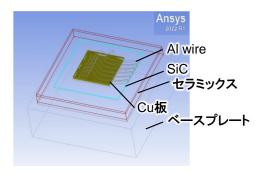

パルス電流によって生じる過渡的な熱の拡がりは、その熱源であるチップ表面における周辺部材の熱容量を増加させることで温度上昇が抑制可能となる。そこで、熱容量を増加させる手段として、SiC-IGBTのエミッタ電極上にはんだを用いてCu板を接合させ、その上にAIワイヤーをボンディングする構造を考案し、過渡熱シミュレーションにて温度上昇が抑制可能か検討した。

図10-1に、従来構造と温度上昇抑制構造の断面模式図を示す。従来構造は、SiC-IGBTチップ裏 面をはんだでCu/セラミックス/Cuからなる絶縁基板へ接合した後、はんだにてベースプレートへ 接合し、SiC-IGBTチップ表面はAIワイヤーをボンディングする。提案構造は、SiC-IGBTチップ裏 面は従来構造と同様とし、SiC-IGBTチップ表面にはんだを用いて追加Cu板を接合した後に、AIワ イヤーをボンディングする。提案構造による温度上昇抑制効果を見積もるため、過渡熱シミュレ ーションを実施した。そのモデルを図10-2に示す。ここでは、SiC-IGBTチップのエミッタ電極と 同面積の追加Cu板をはんだで接合し、昨年度試作した従来モジュール構造と同様のAIワイヤー本 数(ゲート電極用のAIワイヤー1本と、エミッタ電極用のAIワイヤー6本)を追加Cu板上にボンディ ングした構造をモデル化している。また、過渡熱シミュレーションにはAnsys Icepak ver. 2022 R1を用いた。図10-3に従来構造と提案構造の過渡熱シミュレーション結果を示す。チップに入力 した損失は昨年度に実験した10 msecのパルスを入力するテストにてチップが破壊した際のエネ ルギーとした。最大温度を比較すると、従来構造では940℃まで上昇しているのに対し、提案構造 では630℃となり、310℃温度上昇が抑制されるという結果となった。最大温度が300℃低下すれば、 チップ当たりの飽和電流は20-30A程度増加する見込みであり、SiC IGBTミニモデルでのパルスピ 一ク電流1 kAに向けては、従来構造の6チップ並列から1チップ減らし、5チップで実現可能である との見込みを得た。

本検討にて提案した追加Cu板構造は、シミュレーションによる検討のみであり、その実現に向けては、SiC-IGBTチップへ追加Cu板を接合するプロセスを構築しなければならない。SiC-IGBTチップのエミッタ電極の再表面はAIとなっており、このままではCu板のはんだ接合ができないため、Niめっきの検討が必要である。SiC-IGBTチップは100 um程度と非常に薄くなっており、Niめっきプロセスの検討には時間を要するため、本構造の実サンプルへの適用は慎重な検討が必要である。

図 10-1 従来モジュール構造と温度上昇抑制に向けた提案モジュール構造

図 10-2 提案構造の過渡熱 シミュレーションモデル

図 10-3 従来構造と提案構造の過渡 熱シミュレーション結果

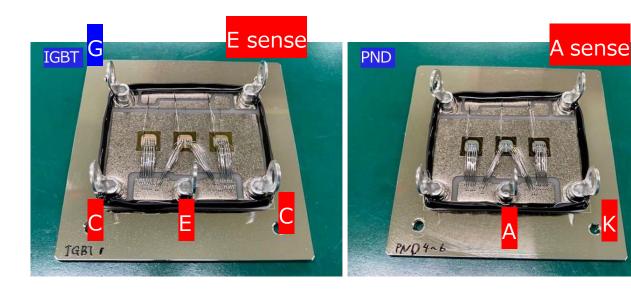

パルス電源動作に向けて、簡易モジュールの作成を行なった。前節で述べた通り、パルスピーク電流1 kAに向けては5チップでの実現可能の見込みを得ているが、モジュール実装の試作歩留まりを考慮し、SiC IGBT及びSiC PND ともに3チップで1モジュールとし、モジュール2台パラレル動作にて5チップ以上の動作をさせることとした。さらに3チップの特性(オン電圧)を $\Delta$ 0.2V 以内の3チップをそろえることでチップ間アンバランスを回避し、モジュールの安定動作実現を図った。図10-5に完成した10kV耐圧簡易パワーモジュール(SiC IGBT及びSiC PND)を示す。モジュール実装は図10-1 に示す従来モジュール構造とした。ワイヤーボンディングは使用線径:  $\phi$ 150  $\mu$  m/ $\phi$ 300  $\mu$ m IGBT: エミッタ×9本 センス×1本 ゲート×1本、PND: アノード×6本センス×1本とした。放電を防止するためにゲル封止し、M5ねじ端子を立てることで電源組み立てに対応させた。

図 10-5 10kV 耐圧簡易パワーモジュールの静特性結果を示す。(室温: SiC IGBT 及び SiC PND)簡易モジュールとしても耐圧10kVを確認し、静特性評価を完了した。この特性を基にピーク電流1kA、1パルスパルス幅10msの試験環境設計を行なった。

図 10-4 10kV 耐圧簡易パワーモジュール (SiC IGBT 及び SiC PND)

図 10-5 10kV 耐圧簡易パワーモジュールの静特性結果 (室温: SiC IGBT 及び SiC PND)

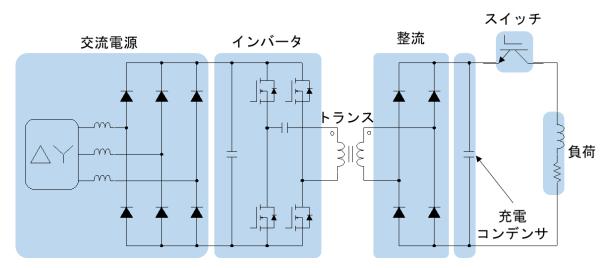

一般的なパルス出力発生回路図を図10-6に示す。このように出力段の電圧をトランスで昇圧し10kV耐圧を形成するのではなく、出力段単体でのパルス動作設計を行なった。電源のブロック図を図10-7に、パルス電源動作試験環境の写真を図10-8に示す。 $SiC\ IGBT,\ SiC\ PND、<math>Si\ PND$ で構成している。結果として3チップモジュール1台にて充電電圧2. 257Kvにてピーク電流1kA、1パルスパルス幅10ms の動作を実現した(図中緑線(Ioutは1/8値))。5チップ必要であると前述しているが、モジュール化した際チップボンディング状態がよくなり熱抵抗が低減したと推測される。

図10-6 一般的なパルス出力発生回路

図 10-7 パルス電源動作回路図

図 10-8 パルス電源動作試験環境

図 10-9 パルス動作試験結果:ピーク電流 1kA、1 パルスパルス幅 10ms

## 4. 委託業務全体の成果

4. 1 計画時に想定していなかった成果(副次的成果)や、目標を超える成果

バイポーラ型パワーデバイスのオン特性に大きな影響を及ぼす少数キャリアライフタイムについて、ジャストエピ技術にライフタイム改善プロセスを適用することで、当初の目標(2 usec)に対して倍の値である4 usecを達成した。本成果は、ジャストエピ技術を超高耐圧SiCパワーデバイスを実用化する際のキーテクノロジーになることを示しており、今後さらなる性能改善を目指していく予定である。

#### 4. 2 研究課題の発展性(間接的成果を含む)

低炭素社会の実現に向けて温暖化ガス排出量を 2050 年に実質ゼロにするグリーン成長戦略が決定された。その中で、2050 年には再生可能エネルギーの比率を今の 3 倍の 50-60%に高める、また 2030 年代半ばまでに、乗用車新車販売で EV100%を実現するという目安が示されている。再生可能エネルギーのなかでも太陽光や風力発電などは自然現象をエネルギー源としている性質上、化石燃料による発電と比べて出力変動が大きい。そして、多数の電動化モビリティが電力ネットワークに接続して双方向の電力融通をするようになると、やはり電力変動が大きくなる。既存の電力ネットワークはそのような出力変動に弱いという課題がある。

小型化・軽量化は、高耐圧・高周波対応可能なパワーモジュールを適用して、商用周波数のトランスを削減することによって実現する。そのようなパワーモジュールは、SiC-IGBT デバイスのスイッチング損失と導通損失のトレードオフ改善による性能革新によって実現する。複数の低耐圧向けフルブリッジインバータの直列接続によっても高耐圧化が可能であるが、この場合は部品点数が多くなってしまい、サイズやコストの増大が避けられない。また、高耐圧 SiC-MOSFET は高周波化の観点で SiC-IGBT より有利であるものの、導通損失が大きいため、大電力用途では SiC-IGBT が有利である。一方、高耐圧 SiC-IGBT を適用した場合の低コスト化については、トランスレス化やモジュール数削減などのプラスの効果があるものの、SiC 適用によるコスト増にも対応する必要がある。

小型化・軽量化・低コスト化実現のため、まずは本開発テーマにて SiC-IGBT デバイスの性能革新と、そのデバイスを用いた構築によって電源系の大幅な小型・軽量化が可能であることを実証した。低コスト SiC-IGBT デバイスの量産技術を確立するとともに、電力ネットワークにつながるシステムを社会実装するためにはシステム信頼性確保が重要であるため、その構成要素であるモジュール信頼性、デバイス信頼性技術を確立して製品化へとつなげていく。パルス電源用途のみならず、洋上風力、EV 急速充電器、電気推進船、電動飛行機、直流データセンタ、高電圧直流送電や各種産業機器等)への適用を検討し、低炭素社会実現に貢献する。

## 4. 3 研究成果の発表・発信に関する活動 特になし

## 5. プロジェクトの総合的推進

5. 1 研究実施体制とマネジメント

プロジェクト全体の連携を密としつつ円滑に運営していくため、プロジェクト全体の進捗状況を確認し、2か月に一回の割合で進捗報告会を実施した。本委託業務の実施により得られた成果について、学会発表、学術論文の投稿、特許出願を行ない、本研究の更なる進展に努めた。なお、研究成果の発表にあたっては、委託契約書の定めに従い事前に発表内容等を通知した。

5. 2 経費の効率的執行 特になし

#### 6. まとめ、今後の予定

① SiCエピ積層構造・ライフタイム制御と高速スイッチングSiC IGBTデバイス設計への適用 手法の確立とデバイス試作 ② SiC IGBT通電劣化現象の解明と抑制の検討を行なった。SiCエピ積層構造・ライフタイム制御と高速スイッチングSiC IGBTデバイス設計への適用手法の確立とデバイス試作、SiC IGBT通電劣化現象の解明と抑制の検討、大電流パルス動作時におけるキャリア再結合のモデル化とキャリアライフタイム制御、積層欠陥のモデル化と電気特性への影響評価 を行なった。設計したSiC IGBTデバイスを試作、耐圧10 kV@1.4  $\mu$ A/cm² 、オン電圧5 V@100 A/cm²を達成するとともにスイッチング動作を実証した。

SiCエピライフタイム制御と高速スイッチングSiC IGBTデバイス設計への適用手法を確立しパルス電源ミニモデル構築向けデバイス試作を行なった。さらに、SiC PNDにおいて局所ライフタイム制御がリカバリ損失低減に効果があることを実証した。SiC IGBT通電劣化現象の解明と抑制の検討を行ない、通電劣化を抑制できる高い通電信頼性を持つコンタクト形成を実証した。SiC IGBTの通流できるパルスピーク電流量最大化手法を構築し、パルス電源ミニモデル構築向けにSiC IGBT・PND搭載基板設計を行なった。設計した基板上に完成したデバイスチップを用い簡易モジュールを試作し完成品の特性測定を実施、パルス電源動作試験環境を設計構築した。最終的に簡易モジュールを用い耐圧10kV、パルスピーク電流1kA、パルス幅10msのパルス動作を実証した。

ジャスト基板を用いたエピ膜成長技術について、3Cインクルージョン抑制のため、成長パラメータの最適化、基板品質との関係性評価、部材の改造等を行った。3Cインクルージョンの抑制が困難であった低螺旋転位密度の基板を用いた成長において、3Cインクルージョンのウェハ全面に対する面積割合 4%を達成した。また、ライフタイム向上のため、ライフタイム低下の原因となる不純物の取り込みの抑制及びライフタイム延伸処理による効果検証を行い、キャリアライフタイム4  $\mu$  secを達成した。PiNダイオードを作製することによりエピ膜の品質評価を行い、順方向劣化が抑制できていることが確認できた。

エピ膜品質を評価するためのSiCサイリスタ構造設計、デバイスプロセス設計を実施し、デバイス試作を行い、デバイス特性の評価を実施することで、エピ膜の品質評価を行った。試作したSiC-GTOサイリスタは、耐電圧値として11.8kV、100A/cm2のオン電圧としてで $11\sim14V$ が得られた。試作したSiC-GTOサイリスタのスイッチング試験を行い、6kV、 $3Aのターンオンおよびターンオフに成功した。さらに、試作したサイリスタが、<math>100kV/\mu$ sの高速なdV/dtにより、ゲート信号なして、アバランシェモードによってターンオンすることが確認できた。そして、大電流パルス試験を実施し、ピーク電流値が157Aの電流を通電することができた。157Aは、1.5kA/cm2の電流密度であり、開発したサイリスタが1kA/cm2を超える大電流を通電できることを示した。

n型およびp型のSiCエピ膜のキャリアライフタイムの温度依存性の測定値を取得して、それぞれに対するキャリア再結合パラメータを求めた。これらのパラメータを用いて、電流密度1 kA/cm²以上までのSiC-IGBTの大電流動作を想定したキャリア再結合モデルを構築し、 $n^-$ 層(耐圧維持層)およびp型層(コレクタ層)のキャリアライフタイムの過剰キャリア密度依存性のモデル計算結果を得た。また、局所キャリアライフタイム制御技術の開発を行い、厚い耐圧維持層中にバナジウム(V)ドープ層を局所的に形成することでキャリアライフタイムを制御できることを確認した。SiC-IGBTの大電流パルス出力時における積層欠陥の拡大の有無や、積層欠陥がデバイスの電気特性に与える影響の評価に関して、デバイス動作温度領域(室温から250°C)での積層欠陥の拡大に関わる物理的パラメータ(積層欠陥エネルギー)を評価するための新たな測定手法を開発するとともに、積層欠陥がデバイスの通電特性に与える影響を表すシミュレーションモデルを構築した。

# 7. 研究発表、知的財産権等の状況

# (1) 研究発表等の状況

| 種別    | 件数   |

|-------|------|

| 学術論文  | 7件   |

| 学会発表  | 18件  |

| 展示・講演 | 該当なし |

| 雑誌・図書 | 該当なし |

| プレス   | 1件   |

| その他   | 該当なし |

# (2) 知的財産権等の状況 別紙5に記載

# (3) その他特記事項 該当なし